RL78/G1H CHAPTER 14 SERIAL ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 415 of 920

Dec 22, 2016

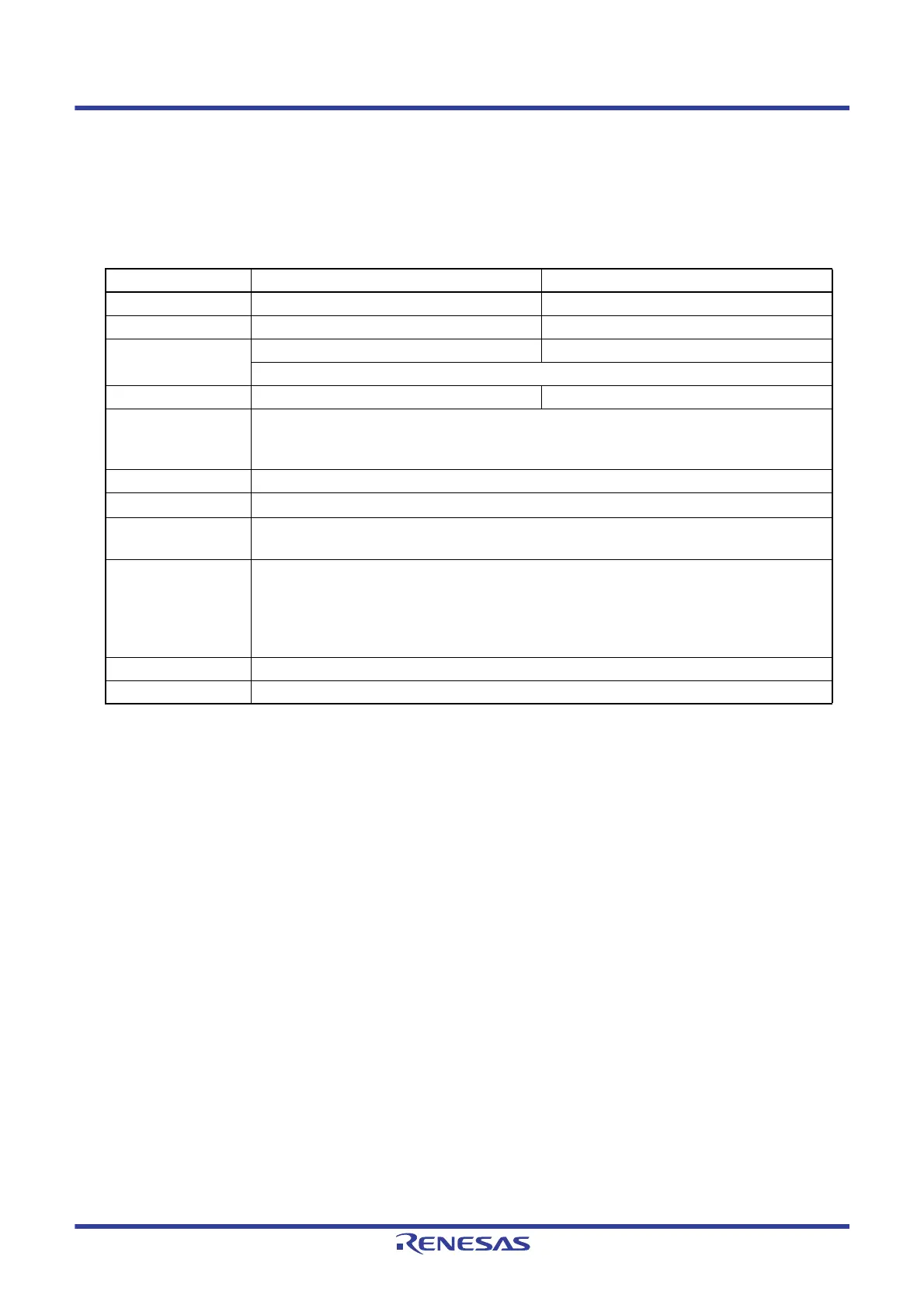

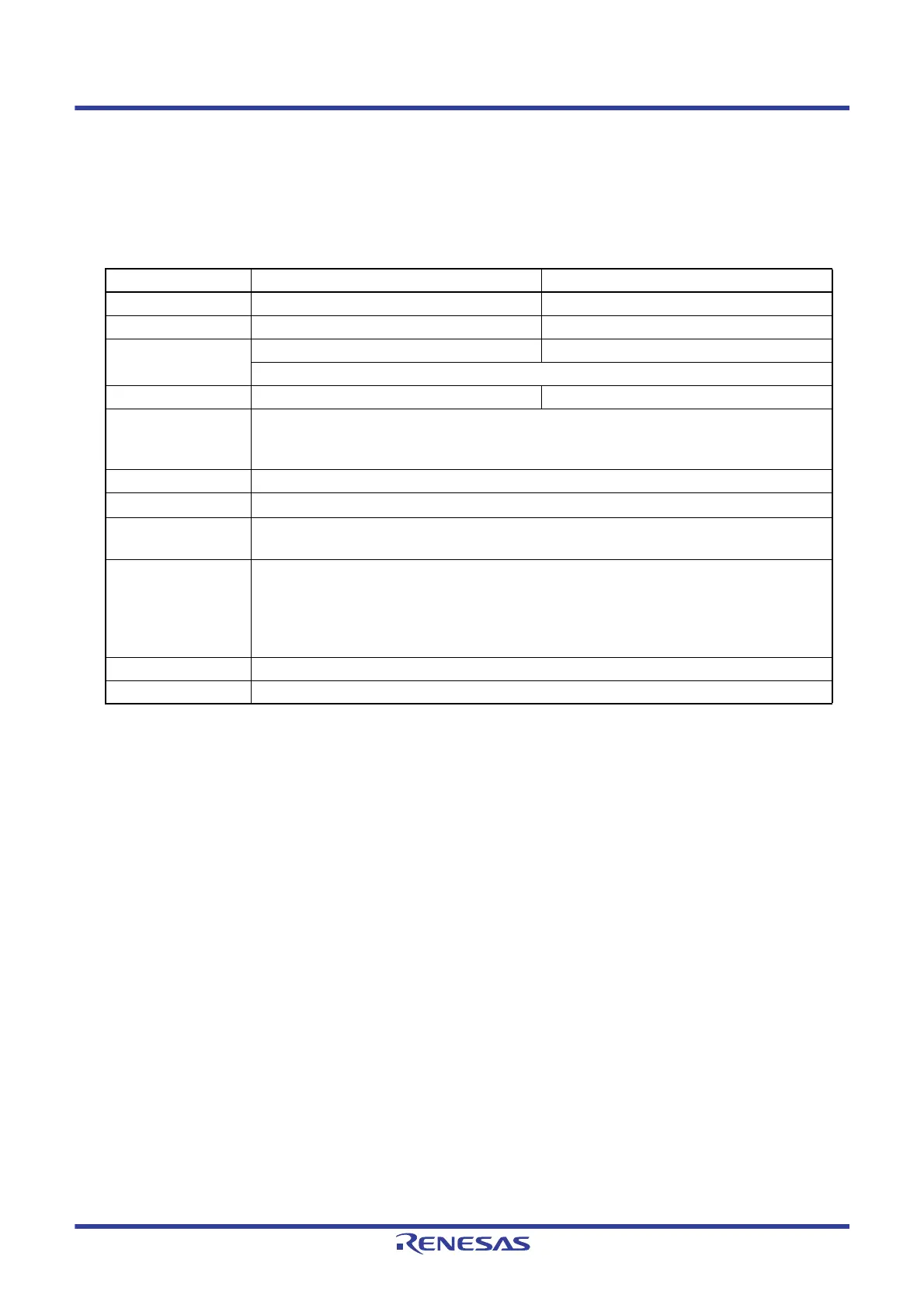

14.6.2 UART reception

UART reception is an operation wherein the RL78 microcontroller asynchronously receives data from another

device (start-stop synchronization).

For UART reception, the odd-number channel of the two channels used for UART is used. The SMR register of

both the odd- and even-numbered channels must be set.

Note Use this operation within a range that satisfies the conditions above and the peripheral functions characteristics in the

electrical specifications (see

CHAPTER 31 ELECTRICAL SPECIFICATIONS).

Remark 1. fMCK:Operation clock frequency of target channel

f

CLK:System clock frequency

Remark 2. m: Unit number (m = 0, 1), n: Channel number (n = 3), mn = 03, 13

UART UART1 UART3

Target channel Channel 3 of SAU0 Channel 3 of SAU1

Pins used RxD1 RxD3

Interrupt INTST1 INTST3

Transfer end interrupt only (Setting the buffer empty interrupt is prohibited.)

Error interrupt INTSRE1 INTSRE3

Error detection flag • Framing error detection flag (FEFmn)

• Parity error detection flag (PEFmn)

• Overrun error detection flag (OVFmn)

Transfer data length 7, or 8 bits

Transfer rate

Note

Max. fMCK/6 [bps] (SDRmn [15:9] = 2 or more), Min. fCLK/(2 × 2

15

× 128) [bps]

Data phase Non-reverse output (default: high level)

Reverse output (default: low level)

Parity bit The following selectable

• No parity bit (no parity check)

• Appending 0 parity (no parity check)

• Appending even parity

• Appending odd parity

Stop bit Appending 1 bit

Data direction MSB or LSB first

Loading...

Loading...