RL78/G1H CHAPTER 7 TIMER ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 167 of 920

Dec 22, 2016

7.3.11 Timer output level register m (TOLm)

The TOLm register is a register that controls the timer output level of each channel.

The setting of the inverted output of channel n by this register is reflected at the timing of set or reset of the timer

output signal while the timer output is enabled (TOEmn = 1) in the Slave channel output mode (TOMmn = 1). In

the master channel output mode (TOMmn = 0), this register setting is invalid.

The TOLm register can be set by a 16-bit memory manipulation instruction.

The lower 8 bits of the TOLm register can be set with an 8-bit memory manipulation instruction with TOLmL.

Reset signal generation clears this register to 0000H.

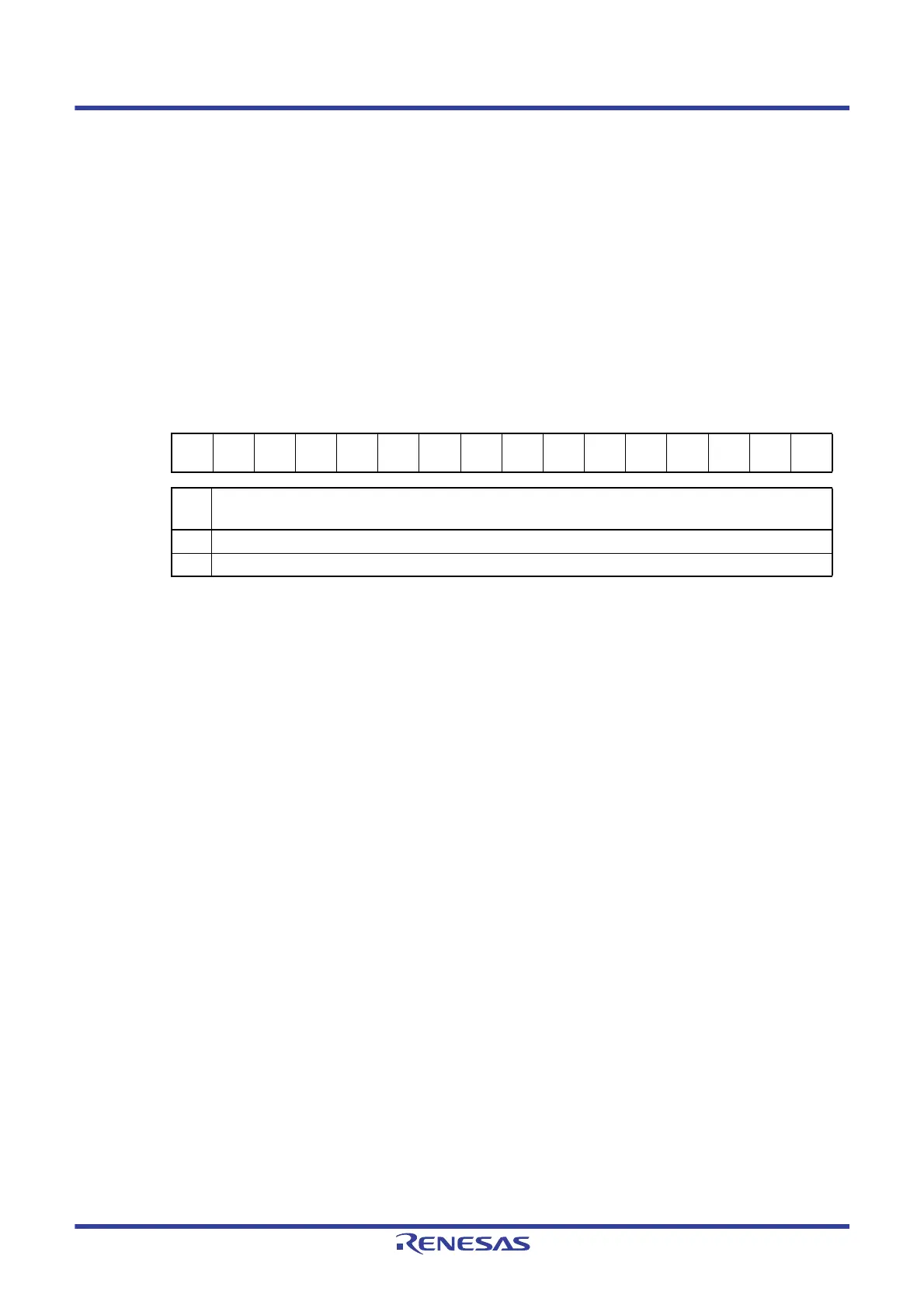

Figure 7 - 23 Format of Timer output level register m (TOLm)

Caution Be sure to clear bits 15 to 4 , 2 to 0 to “0” in TOL0 register. Set to 0000H register in TOL1 register.

Remark 1.

If the value of this register is rewritten during timer operation, the timer output logic is inverted when the timer

output signal changes next, instead of immediately after the register value is rewritten.

Remark 2. m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3)

Address: F01BCH, F01BDH (TOL0), F01FCH, F01FDH (TOL1) After reset: 0000H R/W

Symbol1514131211109876543210

TOLm000000000000

TOLm

3

TOLm

2

TOLm

1

0

TOL

mn

Control of timer output level of channel n

0 Positive logic output (active-high)

1 Negative logic output (active-low)

Loading...

Loading...