RL78/G1H CHAPTER 13 A/D CONVERTER

R01UH0575EJ0120 Rev. 1.20 Page 298 of 920

Dec 22, 2016

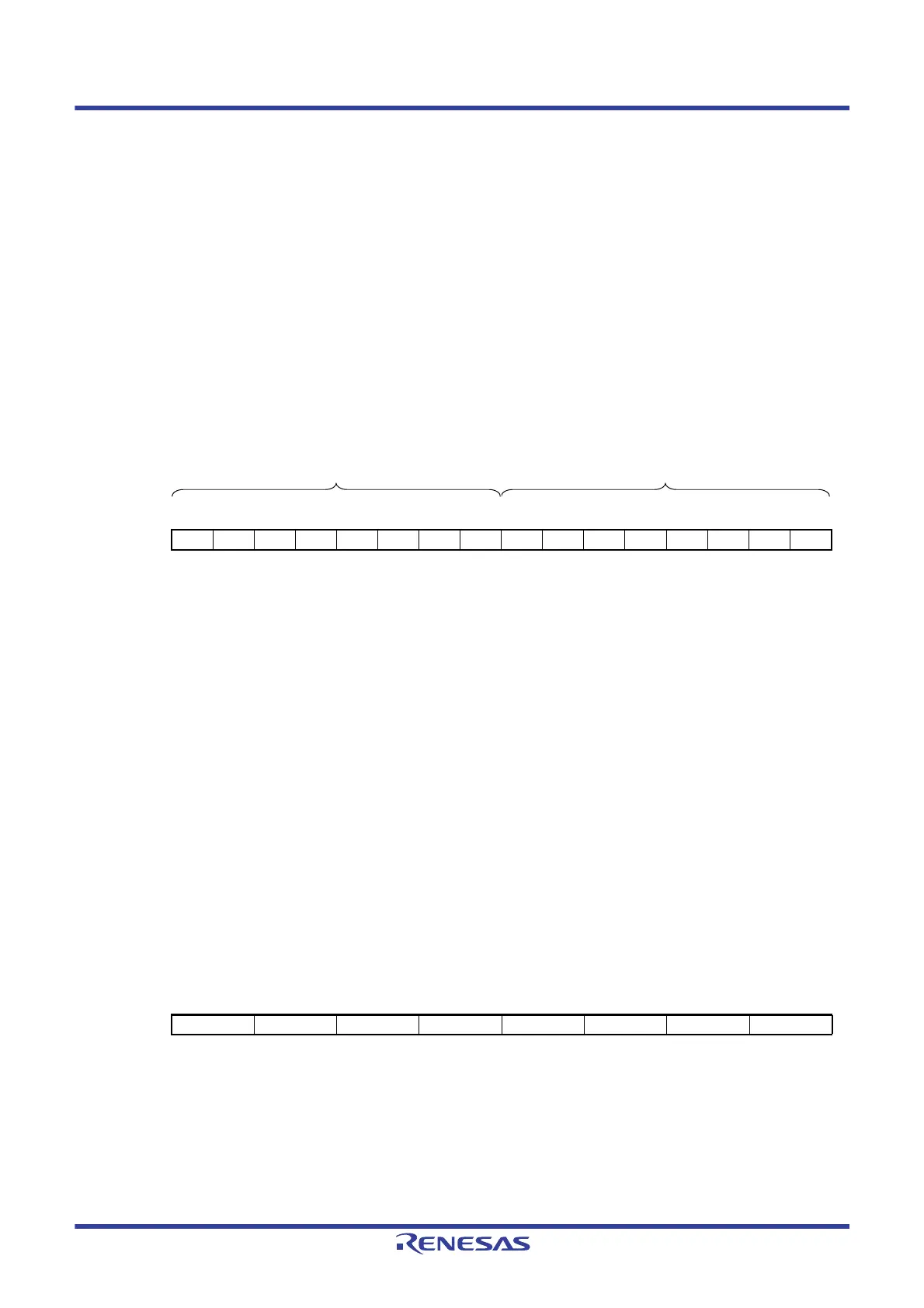

13.3.5 10-bit A/D conversion result register (ADCR)

This register is a 16-bit register that stores the A/D conversion result in the select mode. The lower 6 bits are

fixed to 0. Each time A/D conversion ends, the conversion result is loaded from the successive approximation

register (SAR). The higher 8 bits of the conversion result are stored in FFF1FH and the lower 2 bits are stored in

the higher 2 bits of FFF1EH

Note

.

The ADCR register can be read by a 16-bit memory manipulation instruction.

Reset signal generation clears this register to 0000H.

Note If the A/D conversion result is outside the range specified by using the A/D conversion comparison

function (the value specified by the ADRCK bit of the ADM2 register and ADUL/ADLL registers; see

Figure 13 - 9), the result is not stored.

Figure 13 - 10 Format of 10-bit A/D conversion result register (ADCR)

Caution 1. When 8-bit resolution A/D conversion is selected (when the ADTYP bit of A/D converter mode

register 2 (ADM2) is 1) and the ADCR register is read, 0 is read from the lower two bits (bits 7 and 6 of

the ADCR register).

Caution 2. When the ADCR register is accessed in 16-bit units, the higher 10 bits of the conversion result are

read in order starting at bit 15.

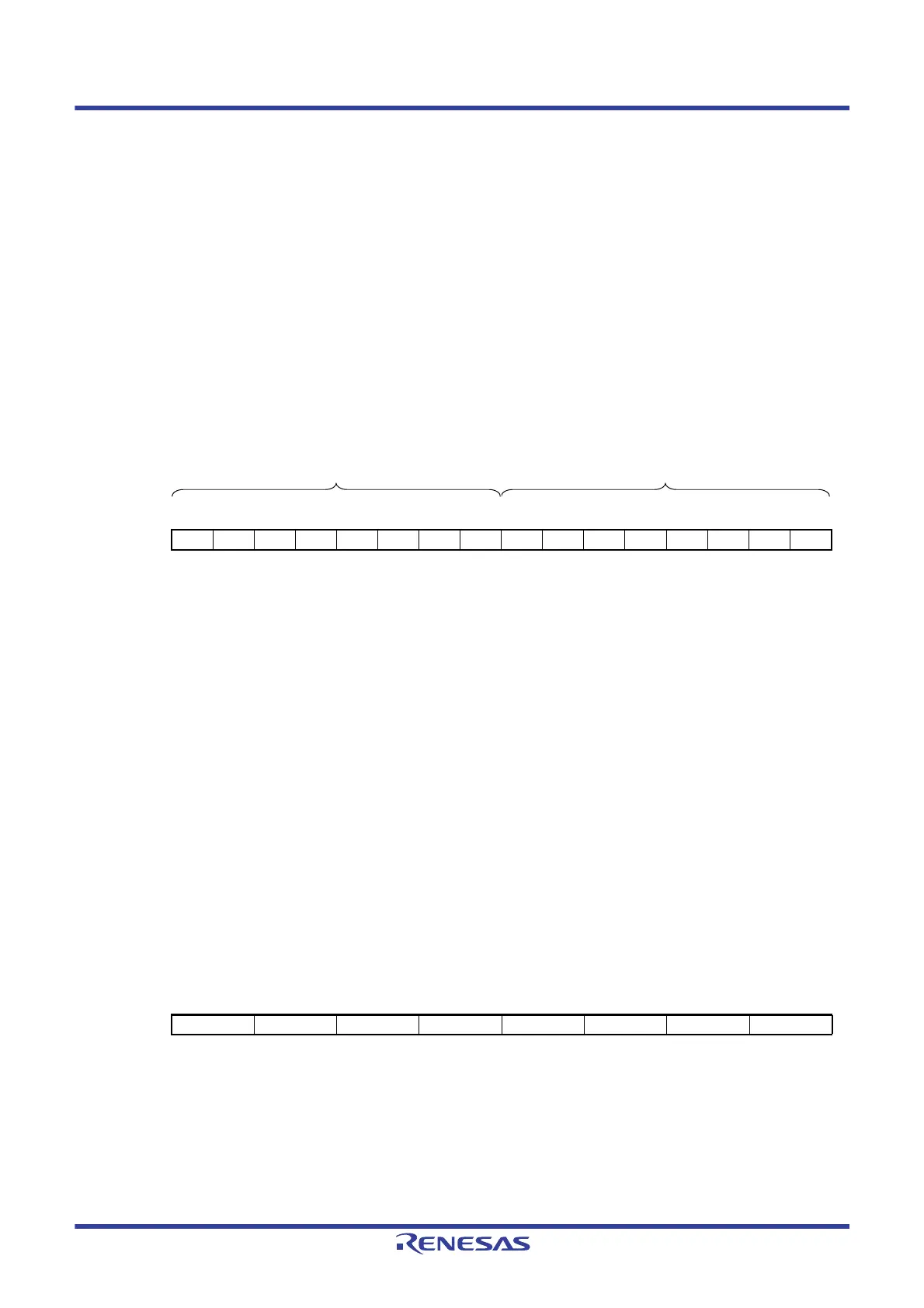

13.3.6 8-bit A/D conversion result register (ADCRH)

This register is an 8-bit register that stores the A/D conversion result. The higher 8 bits of 10-bit resolution are

stored

Note

.

The ADCRH register can be read by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Note If the A/D conversion result is outside the range specified by using the A/D conversion comparison

function (the value specified by the ADRCK bit of the ADM2 register and ADUL/ADLL registers; see

Figure 13 - 9), the result is not stored.

Figure 13 - 11 Format of 8-bit A/D conversion result register (ADCRH)

Caution When writing to the A/D converter mode register 0 (ADM0), Analog input channel specification

register (ADS), and A/D port configuration register (ADPC), the contents of the ADCRH register may

become undefined. Read the conversion result following conversion completion before writing to the

ADM0, ADS, and ADPC registers. Using timing other than the above may cause an incorrect

conversion result to be read.

Address: FFF1FH, FFF1EH After reset: 0000H R

Symbol FFF1FH FFF1EH

1514131211109876543210

ADCR 000000

Address: FFF1FH After reset: 00H R

Symbol76543210

ADCRH

Loading...

Loading...