RL78/G1H CHAPTER 16 DATA TRANSFER CONTROLLER (DTC)

R01UH0575EJ0120 Rev. 1.20 Page 534 of 920

Dec 22, 2016

16.4.4 Chain Transfers

When the CHNE bit in the DTCCRj (j = 0 to 22) register is 1 (chain transfers enabled), multiple data transfers can

be continuously performed by one activation source.

When the DTC is activated, one control data is selected according to the data read from the vector address

corresponding to the activation source, and the selected control data is read from the DTC control data area.

When the CHNE bit for the control data is 1 (chain transfers enabled), the next control data immediately following

the current control data is read and transferred after the current transfer is completed. This operation is repeated

until the data transfer with the control data for which the CHNE bit is 0 (chain transfers disabled) is completed.

When chain transfers are performed using multiple control data, the number of transfers set for the first control

data is enabled, and the number of transfers set for the second and subsequent control data to be processed will

be invalid.

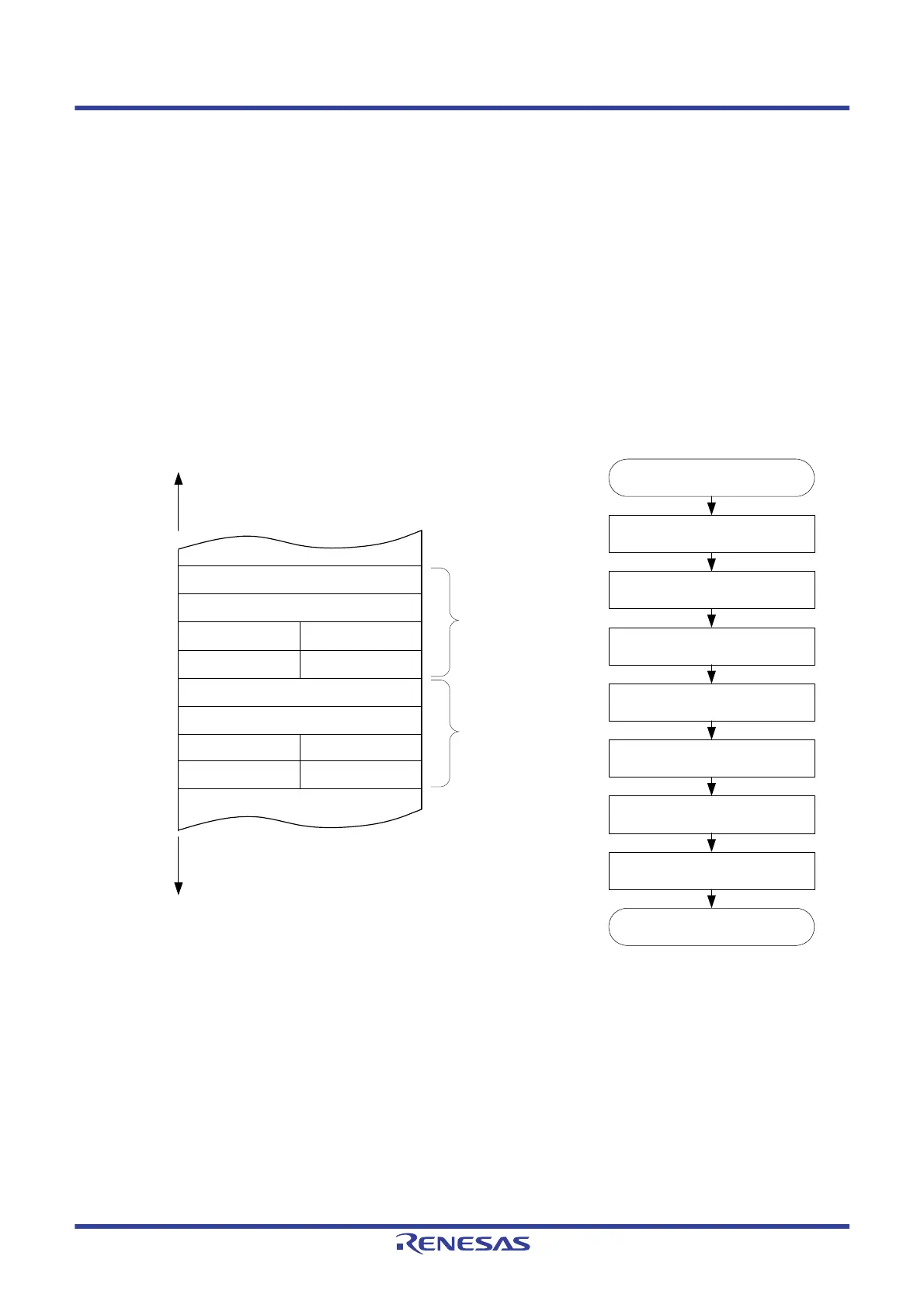

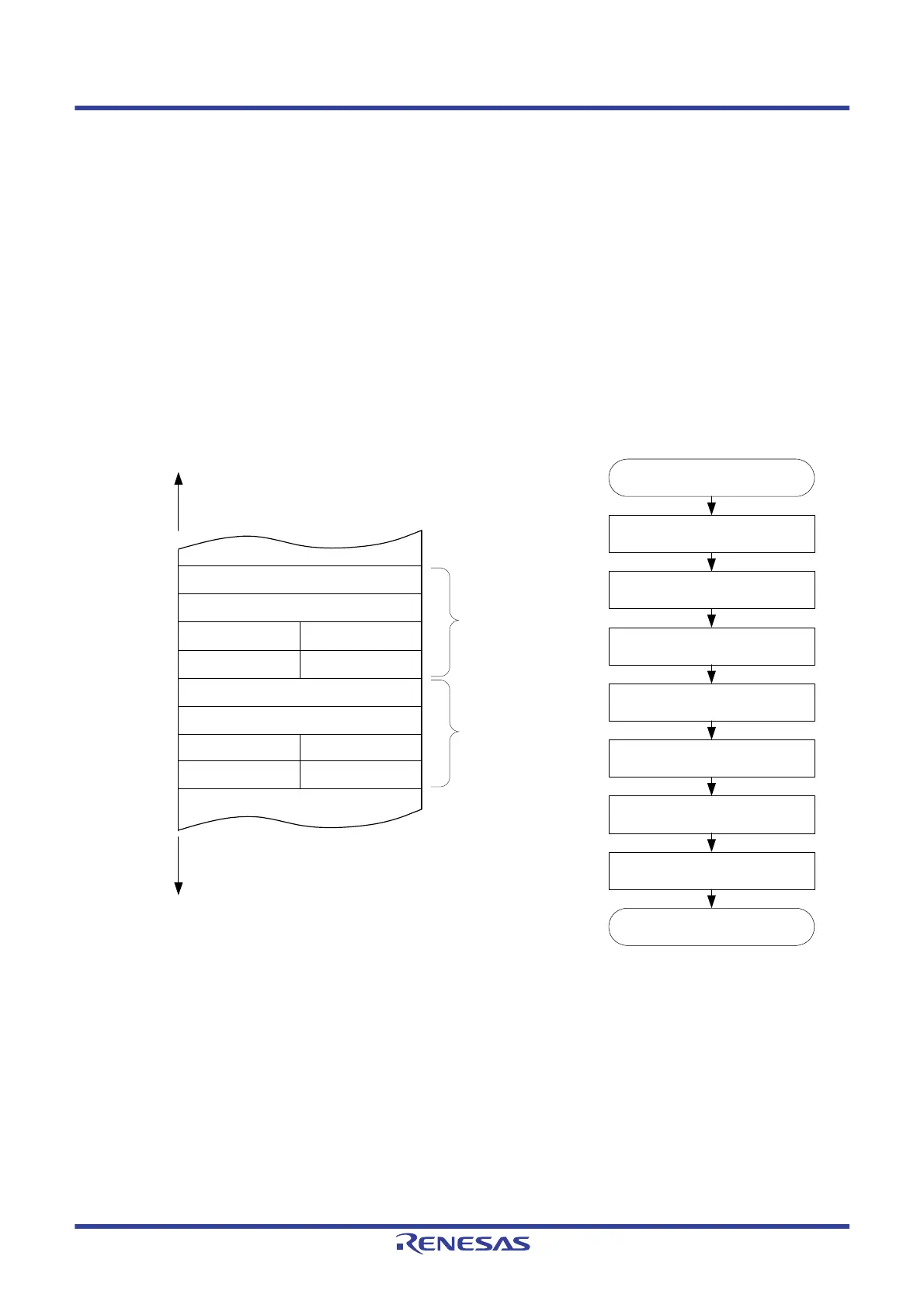

Figure 16 - 17 shows Data Transfers during Chain Transfers.

Figure 16 - 17 Data Transfers during Chain Transfers

Caution 1. Set the CHNE bit in the DTCCR23 register to 0 (chain transfers disabled).

Caution 2. During chain transfers, bits DTCENi0 to DTCENi7 (i = 0 to 4) in the DTCENi register are not set to 0 (activation

disabled) for the second and subsequent transfers. Also, no interrupt request is generated.

FFFFFH

DTDAR2 register

DTSAR2 register

DTRLD2 register DTCCT2 register

DTBLS2 register

DTCCR2 register

DTDAR1 register

DTSAR1 register

DTRLD1 register

DTCCT1 register

DTBLS1 register

DTCCR1 register

F0000H

Control data 1

(the CHNE bit is 1)

Control data 2

(the CHNE bit is 0)

DTC activation source generation

Read vector

Read control data 1

Transfer data

Write back control data 1

Read control data 2

Transfer data

Write back control data 2

End of DTC transfers

Lower addressHigher address

Loading...

Loading...