RL78/G1H CHAPTER 19 INTERRUPT FUNCTIONS

R01UH0575EJ0120 Rev. 1.20 Page 720 of 920

Dec 22, 2016

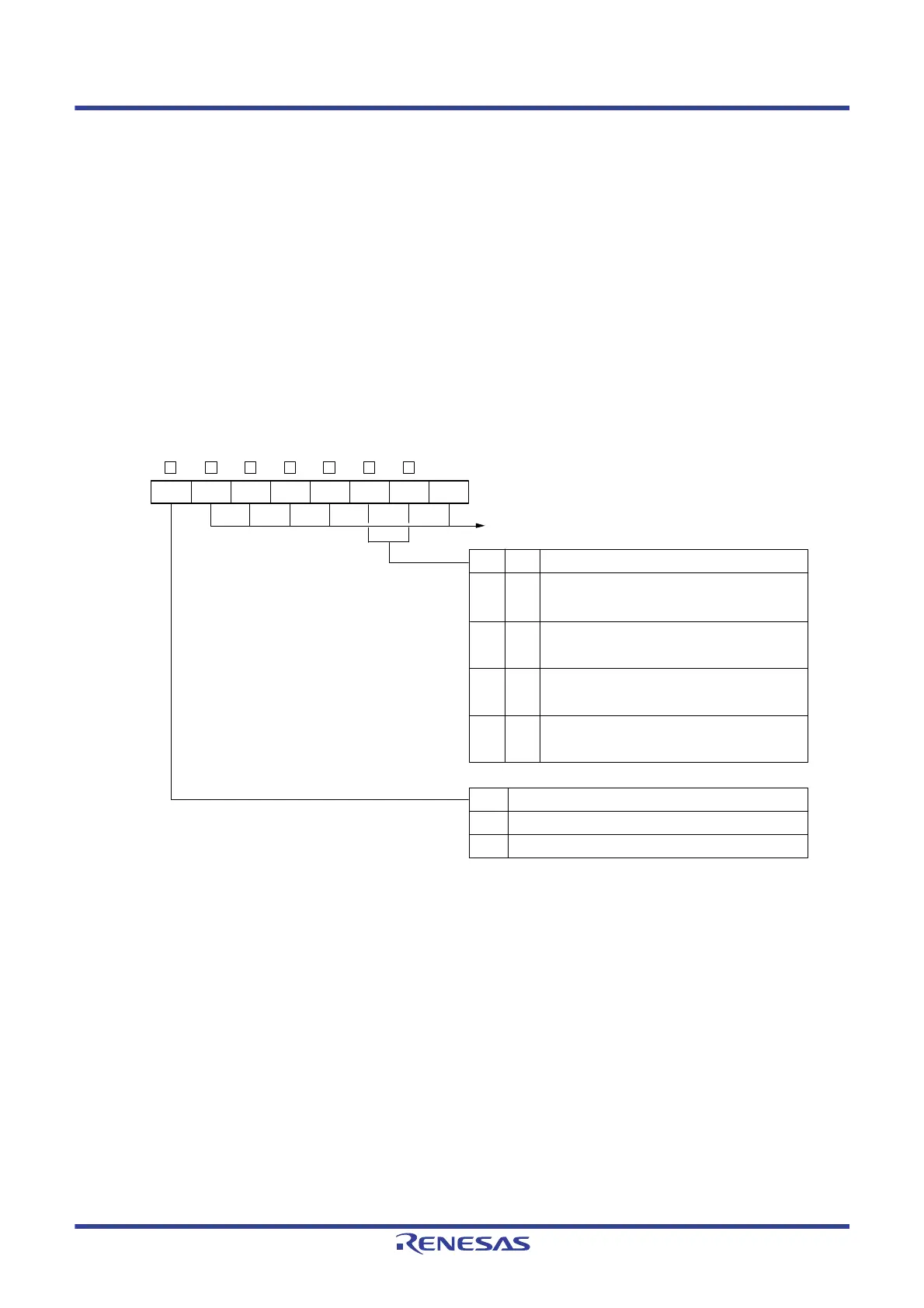

19.3.5 Program status word (PSW)

The program status word is a register used to hold the instruction execution result and the current status for an

interrupt request. The IE flag that sets maskable interrupt enable/disable and the ISP0 and ISP1 flags that

controls multiple interrupt servicing are mapped to the PSW.

Besides 8-bit read/write, this register can carry out operations using bit manipulation instructions and dedicated

instructions (EI and DI). When a vectored interrupt request is acknowledged, if the BRK instruction is executed,

the contents of the PSW are automatically saved into a stack and the IE flag is reset to 0. Upon acknowledgment

of a maskable interrupt request, if the value of the priority specification flag register of the acknowledged interrupt

is not 00, its value minus 1 is transferred to the ISP0 and ISP1 flags. The PSW contents are also saved into the

stack with the PUSH PSW instruction. They are restored from the stack with the RETI, RETB, and POP PSW

instructions.

Reset signal generation sets PSW to 06H.

Figure 19 - 9 Configuration of Program Status Word

IE

0

PSW

After reset

06H

ISP1

0

Enables all interrupts

(waits for acknowledgment of an interrupt).

Disabled

Enabled

Priority of interrupt currently being serviced

Interrupt request acknowledgment enable /disable

Used when normal instruction is executed

6 5 4 3 17 2

ISP0

0

Z RBS1 AC RBS0 ISP1 ISP0 CY

01

10

11

IE

0

1

Enables interrupt of level 0 to 2

(while interrupt of level 3 is being serviced).

Enables interrupt of level 0 and 1

(while interrupt of level 2 is being serviced).

Enables interrupt of level 0

(while interrupt of level 1 or 0 is being serviced).

Loading...

Loading...