RL78/G1H CHAPTER 10 12-BIT INTERVAL TIMER

R01UH0575EJ0120 Rev. 1.20 Page 263 of 920

Dec 22, 2016

10.3.2 Subsystem clock supply mode control register (OSMC)

The WUTMMCK0 bit can be used to select the 12-bit interval timer, real-time clock, and timer RJ operation clock.

In addition, by stopping clock functions that are unnecessary, the RTCLPC bit can be used to reduce power

consumption. For details about setting the RTCLPC bit, see CHAPTER 6 CLOCK GENERATOR.

The OSMC register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

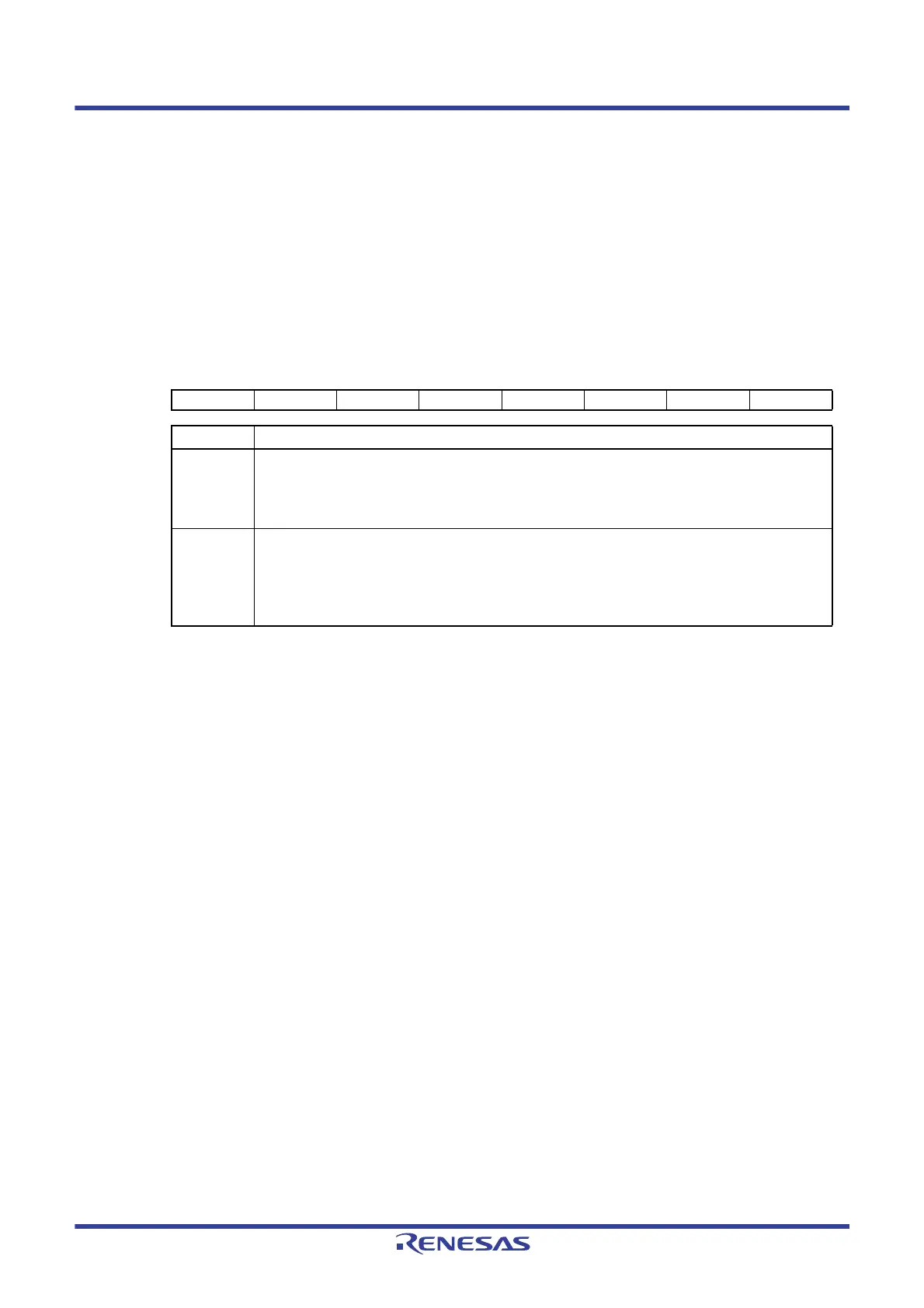

Figure 10 - 3 Format of Subsystem clock supply mode control register (OSMC)

Address: F00F3H After reset: 00H R/W

Symbol76543210

OSMC RTCLPC 0 0 WUTMMCK0 0 0 0 0

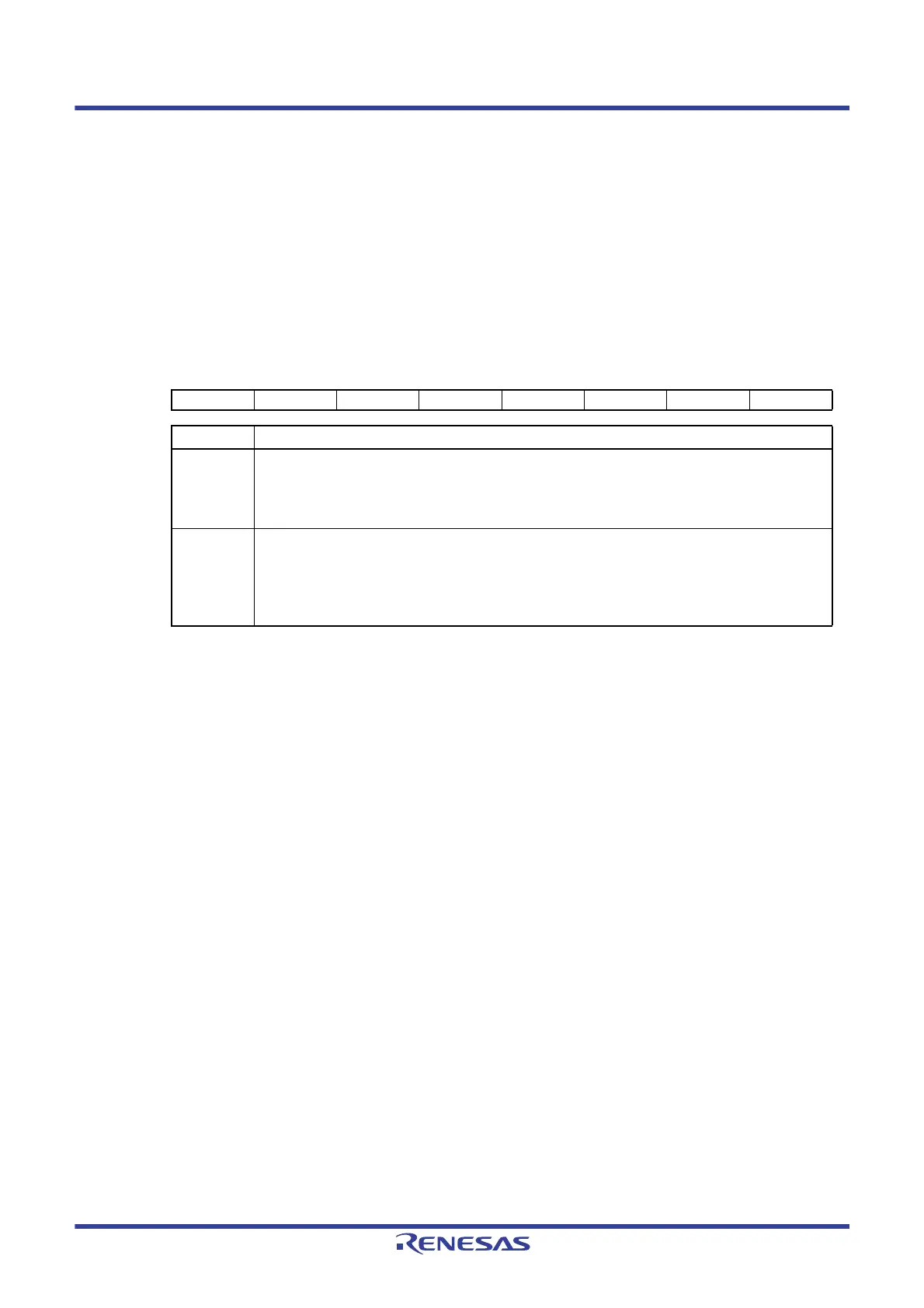

WUTMMCK0 Selection of operation clock for real-time clock, 12-bit interval timer, and timer RJ.

0 Subsystem clock (f

SUB)

• The subsystem clock is selected as the operation clock for the real-time clock and the 12- bit interval

timer.

• The low-speed on-chip oscillator cannot be selected as the count source for timer RJ.

1 Low-speed on-chip oscillator clock (f

IL)

• The low-speed on-chip oscillator clock is selected as the operation clock for the real-time clock and the

12-bit interval timer.

• Either the low-speed on-chip oscillator or the subsystem clock can be selected as the count source for

timer RJ.

Loading...

Loading...