RL78/G1H CHAPTER 6 CLOCK GENERATOR

R01UH0575EJ0120 Rev. 1.20 Page 105 of 920

Dec 22, 2016

6.3.3 Clock operation status control register (CSC)

This register is used to control the operations of the high-speed system clock, high-speed on-chip oscillator

clock, and subsystem clock (except the low-speed on-chip oscillator clock).

The CSC register can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to C0H.

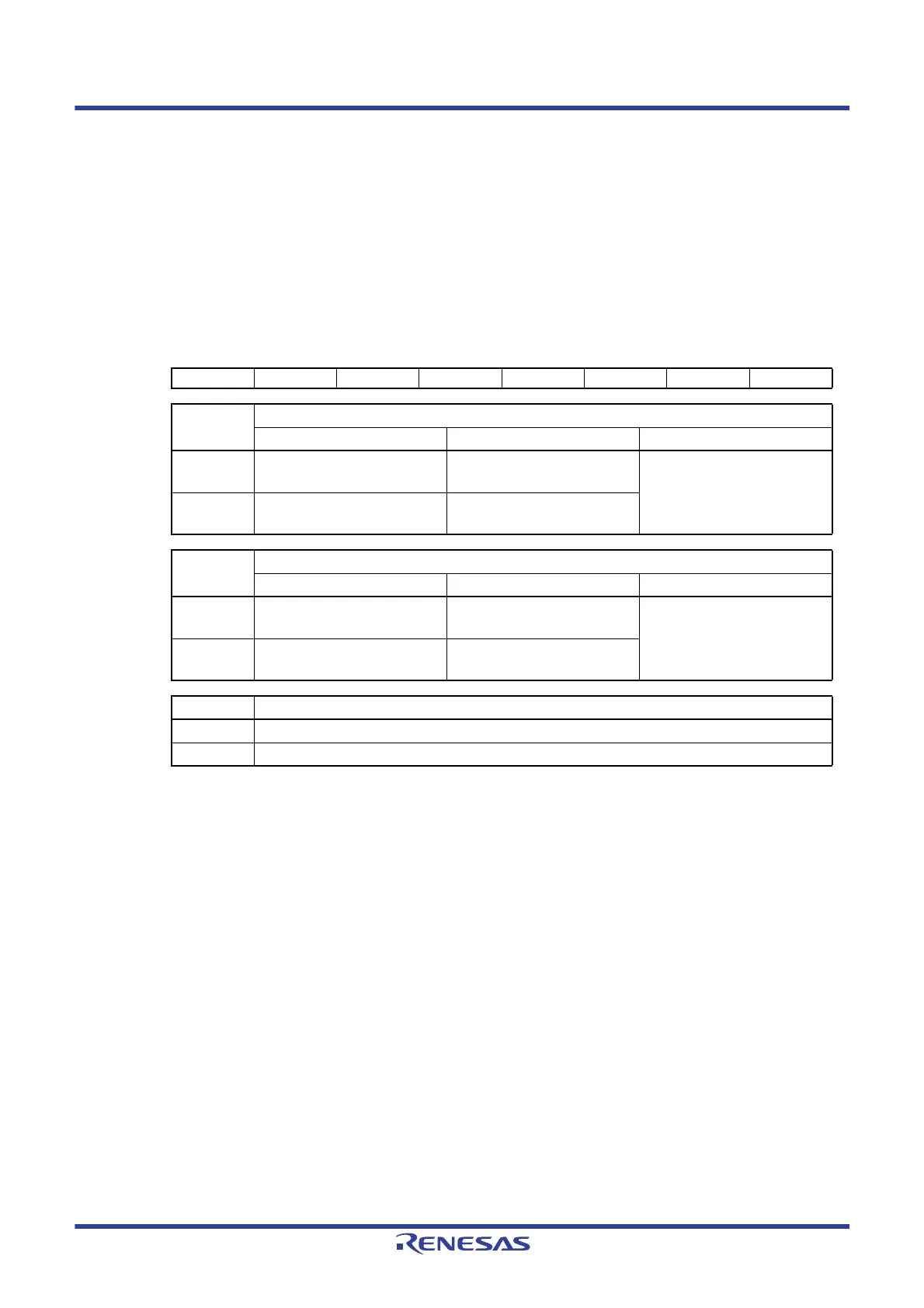

Figure 6 - 4 Format of Clock operation status control register (CSC)

Caution 1. After reset release, set the clock operation mode control register (CMC) before setting the CSC

register.

Caution 2. Set the oscillation stabilization time select register (OSTS) before setting the MSTOP bit to 0 after

releasing reset. Note that if the OSTS register is being used with its default settings, the OSTS

register is not required to be set here.

Caution 3. To start X1 oscillation as set by the MSTOP bit, check the oscillation stabilization time of the X1 clock

by using the oscillation stabilization time counter status register (OSTC).

Caution 4. When starting XT1 oscillation by setting the XSTOP bit, wait for oscillation of the subsystem clock to

stabilize by setting a wait time using software.

Caution 5. Do not stop the clock selected for the CPU peripheral hardware clock (f

CLK) with the OSC register.

Caution 6. The setting of the flags of the register to stop clock oscillation (invalidate the external clock input)

and the condition before clock oscillation is to be stopped are as Table 6 - 2. Check the condition

before stopping clock before stopping the clock.

Address: FFFA1H After reset: C0H R/W

Symbol<7><6>54321<0>

CSCMSTOPXTSTOP00000HIOSTOP

MSTOP

High-speed system clock operation control

X1 oscillation mode External clock input mode Input port mode

0 X1 oscillator operating External clock from EXCLK pin is

valid

Input port

1 X1 oscillator stopped External clock from EXCLK pin is

invalid

XTSTOP

Subsystem clock operation control

XT1 oscillation mode External clock input mode Input port mode

0 XT1 oscillator operating External clock from EXCLKS pin

is valid

Input port

1 XT1 oscillator stopped External clock from EXCLKS pin

is invalid

HIOSTOP High-speed on-chip oscillator clock operation control

0 High-speed on-chip oscillator operating

1 High-speed on-chip oscillator stopped

Loading...

Loading...