RL78/G1H CHAPTER 18 RF TRANSCEIVER

R01UH0575EJ0120 Rev. 1.20 Page 622 of 920

Dec 22, 2016

(55) SUBG control register (BBSUBGCON)

This register is used to control the SubGHz transceiver.

The FEC enable bit for reception is used to enable FEC (CODE) of reception.

The FEC mode switch bit is used to switch the FEC encode mode.

The number-of-CRC-bit switch bit is used to switch the number of bits for the CRC calculation process upon

transmission. Note that the number of the CRC bits of the receive frame is used for those upon auto-ACK

reply.

The DW enable bit is used to enable the data whitening upon transmission.

The PHR transmit bit 1 is used to transmit bit 1 of the PHR upon transmission.

The PHR transmit bit 2 is used to transmit bit 2 of the PHR upon transmission.

The interleaving enable bit is used to enable the interleaving. Set INTERLEAVEEN bit to 1 to use FEC.

The BBSUBGCON register is set by the serial interface in 8-bit units.

Reset signal generation sets this register to 0CH.

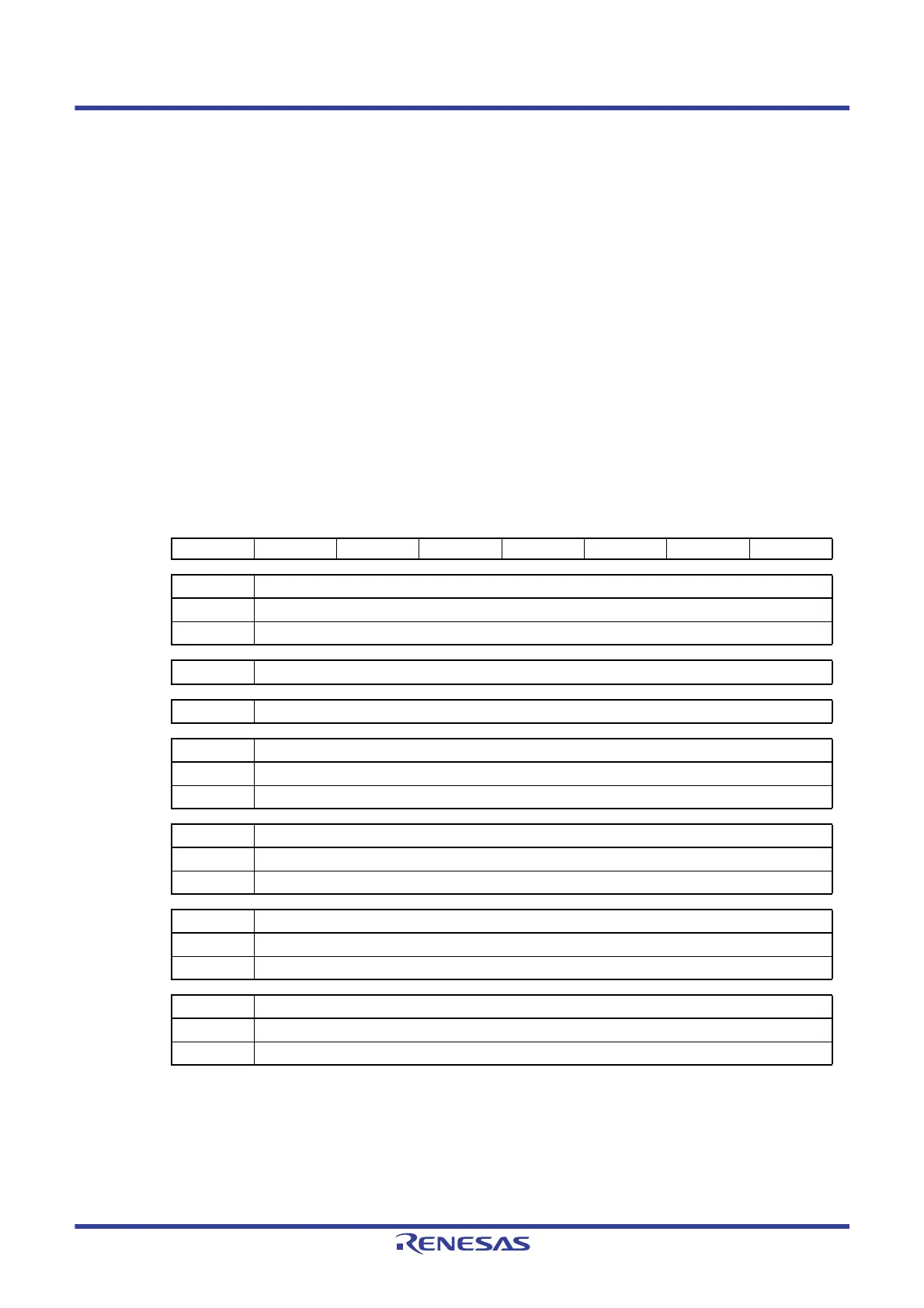

Figure 18 - 68 SUBG Control Register (BBSUBGCON) Format

Caution Be sure to clear bit 7 to "0".

Address: 00B0H After reset: 0CH R/W

Symbol76543210

BBSUBGCON

0

INTERLEAVEEN

PHRTX2 PHRTX1 DWEN CRCBIT FECMODE FECENRX

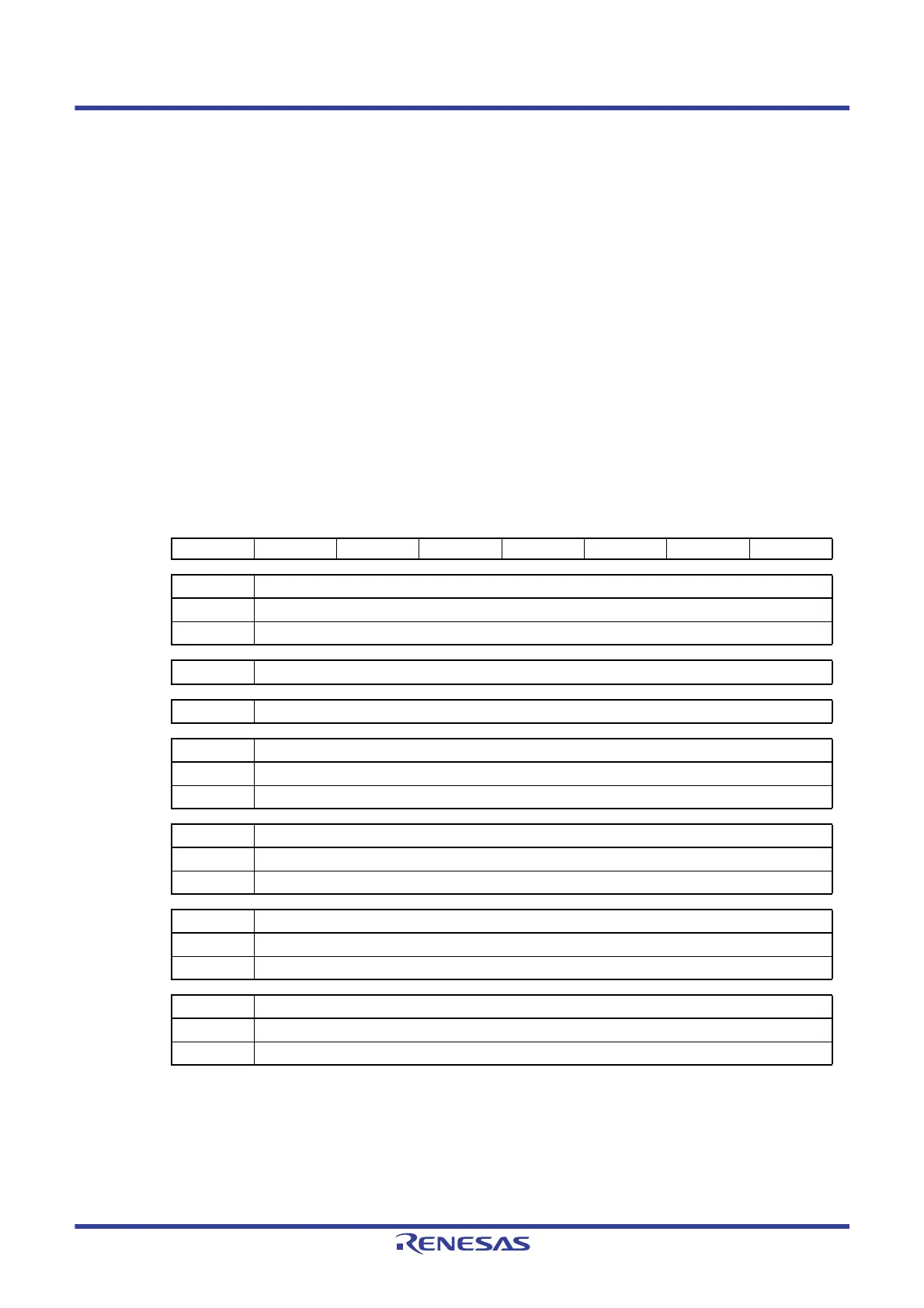

INTERLEAVEEN

Interleaving enable bit

0 Interleaving disabled

1 Interleaving enabled

PHRTX2 PHR transmission bit 2 value

PHRTX1 PHR transmission bit 1 value

DWEN DW enable bit

0 DW disabled

1 DW enabled

CRCBIT Number-of-CRC-bit switch bit

0 32-bit CRC

1 16-bit CRC

FECMODE FEC mode switch bit

0 NRNSC encoder

1 RSC encoder

FECENRX FEC enable bit for reception

0 FEC disabled

1 FEC enabled

Loading...

Loading...