4.74

SEL-751A Relay Instruction Manual Date Code 20100129

Protection and Logic Functions

Reclose Logic

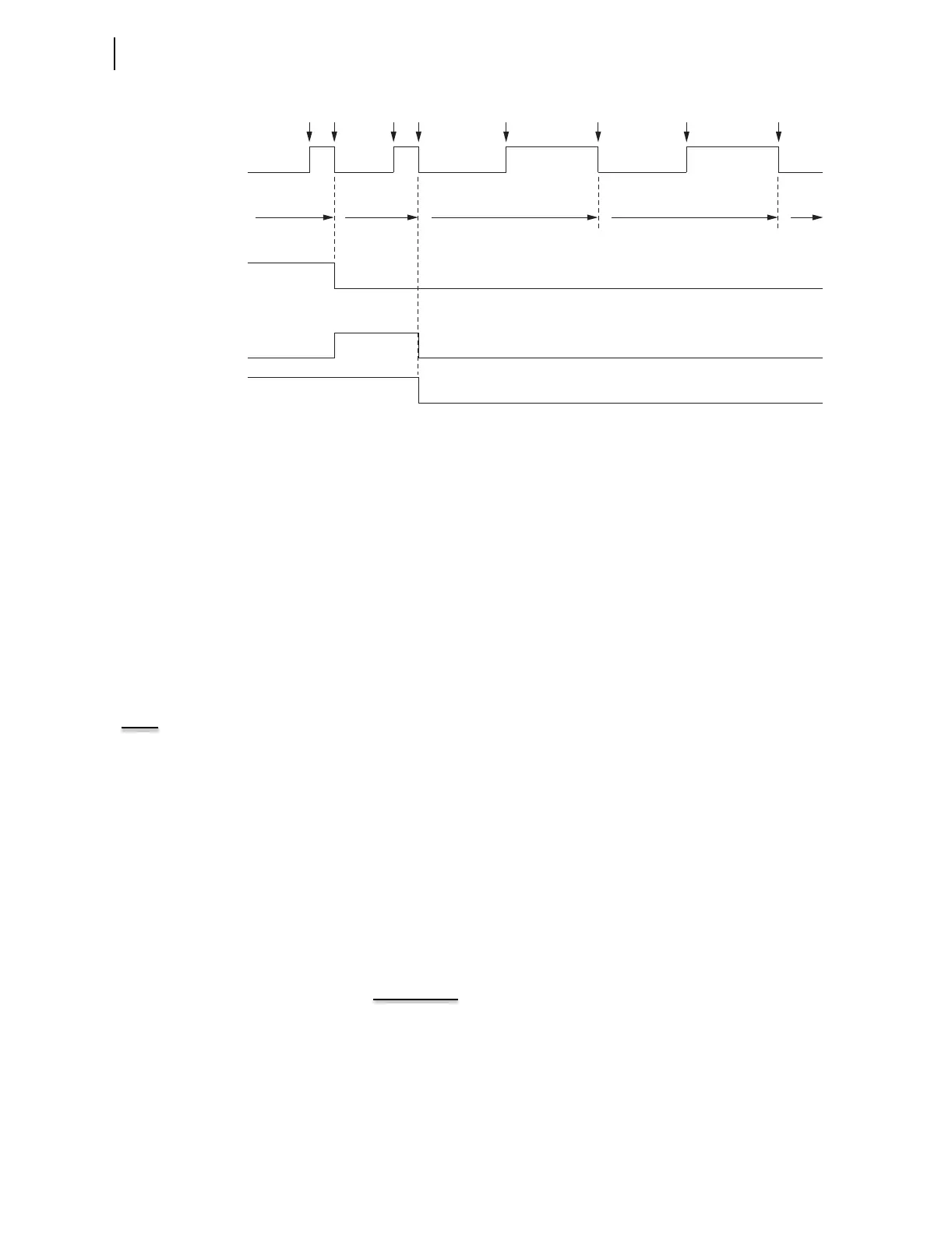

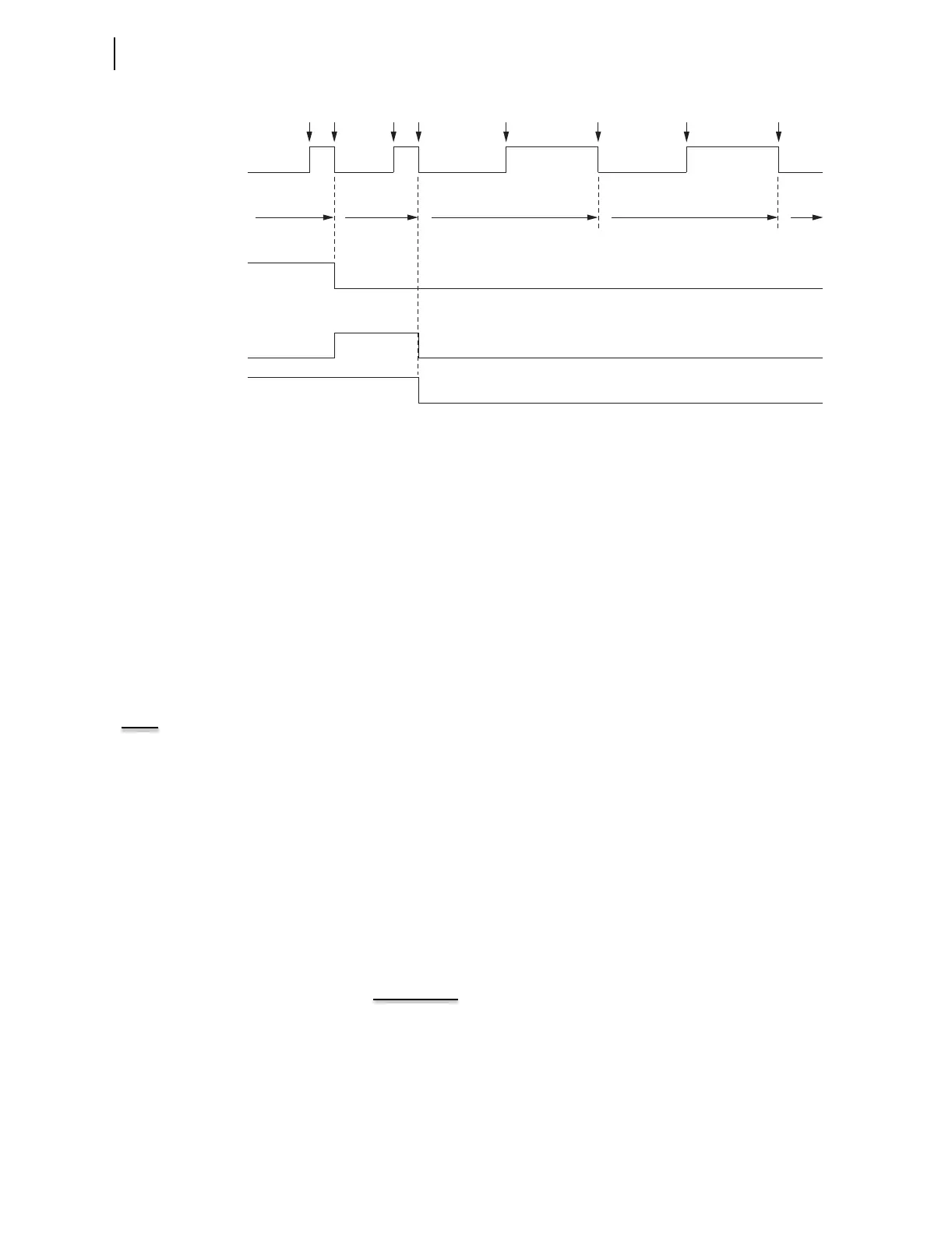

q Fault occurs beyond line recloser; w fault cleared by line recloser fast curve; e line recloser recloses into fault; r fault

cleared by line recloser slow curve.

Figure 4.38 Operation of SEL-751A Shot Counter for Sequence Coordination With Line Recloser (Additional

Settings Example 1)

If the SEL-751A is in the Reset State (79RS = logical 1) and then a

permanent fault beyond the line recloser occurs (fault current I

F

in

Figure 4.37), the line recloser fast curve operates to clear the fault.

The SEL-751A also sees the fault. The phase time-overcurrent pickup

51P1P asserts and then deasserts without tripping, incrementing the

relay shot counter from:

shot = 0 to shot = 1

When the line recloser recloses its circuit breaker, the line recloser

fast curve operates again to clear the fault. The SEL-751A also sees

the fault again. The phase time-overcurrent pickup 51P1P asserts and

then deasserts without tripping, incrementing the relay shot counter

from:

shot = 1 to shot = 2

The line recloser fast curve is now disabled after operating twice.

When the line recloser recloses its circuit breaker, the line recloser

slow curve operates to clear the fault. The relay does not operate on

its faster-set phase time-overcurrent element 51P1 (51P1T is “below”

the line recloser slow curve) because the shot counter is now at shot

= 2. For this sequence coordination scheme, the SEL

OGIC control

equation trip equation is:

TR := 51P1T AND (SH0 OR SH1) OR 51AT OR 51BT OR 51CT

With the shot counter at shot = 2, Relay Word bits SH0 (shot = 0) and

SH1 (shot = 1) are both deasserted to logical 0. This keeps the 51PT

phase time-overcurrent element from tripping. The 51P1T phase time-

overcurrent element is still operative, and its pickup (51P1P) can still

assert and then deassert, thus continuing the sequencing of the shot

counter to shot = 3, etc. The 51P1T phase time-overcurrent element

cannot cause a trip because shot ≥ 2, and SH0 and SH1 both are

deasserted to logical 0.

The shot counter returns to shot = 0 after the reset timer (loaded

with reset time 79RSD) times out.

EXAMPLE 4.20 Additional Settings Example 2

Review preceding Example 1.

Assume that the line recloser in Figure 4.37 is set to operate twice on

the fast curve and then twice on the slow curve for faults beyond the

line recloser.

Assume that the SEL-751A is set to operate once on 51P1T and then

twice on 51AT, 51BT, or 51CT for faults between the SEL-751A and the

line recloser. This results in the following trip setting:

79SEQ := 79RS AND 51P1P

SH0 OR SH1

SH1

SH0

Shot Counter 0 1 2 3

4

qw ew e r e r

NOTE: Sequence coordination can

increment the shot counter beyond

last shot in this example (last shot = 2

in this factory setting example) but no

further than shot = 4.

The following Example 2 limits

sequence coordination shot counter

incrementing.

Loading...

Loading...