7.40

SEL-751A Relay Instruction Manual Date Code 20100129

Communications

SEL ASCII Protocol and Commands

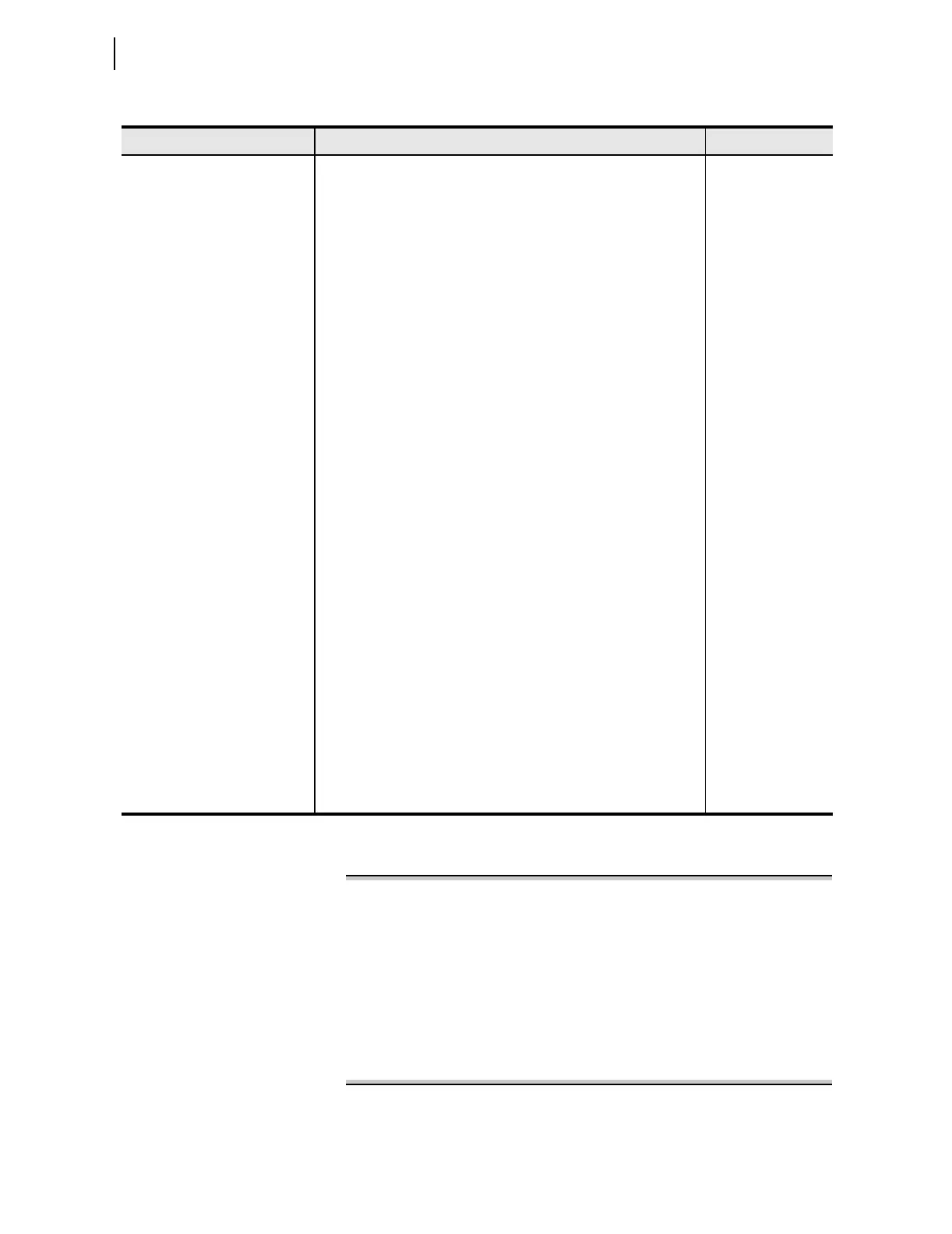

Figure 7.22 shows the typical relay output for the STATUS S command,

showing available SEL

OGIC control equation capability.

=>STA S <Enter>

SEL-751A Date: 02/27/2007 Time: 15:04:16

FEEDER RELAY Time Source: Internal

Part Number 751A01BBX5X7186030X

Global (%) 81

FP (%) 69

Report (%) 96

GROUP 1 GROUP 2 GROUP 3

Execution (%) 90 90 90

Group (%) 81 81 81

Logic (%) 89 89 89

=>

Figure 7.22 Typical Relay Output for STATUS Command

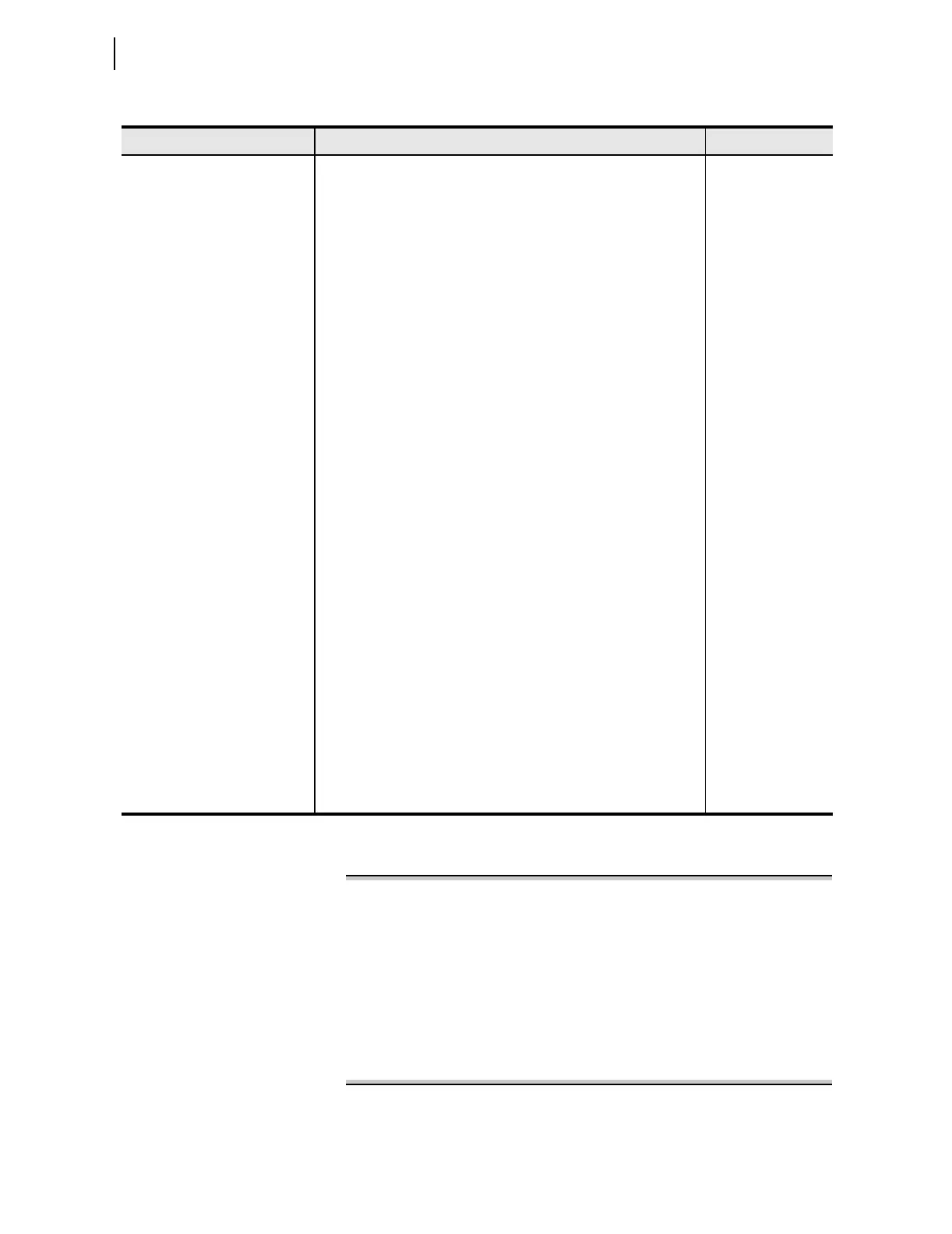

Table 7.47 STATUS Command Report and Definitions

STATUS Report Designator Definition Message Format

Serial Num Serial number Number

FID Firmware identifier string Text Data

CID Firmware checksum identifier Hex

PART NUM Part number Text Data

FPGA FPGA programming unsuccessful, or FPGA failed OK/FAIL

GPSB General Purpose Serial Bus OK/FAIL

HMI Front-Panel FGPA programming unsuccessful, or Front-Panel FPGA

failed

OK/WARN

RAM Volatile memory integrity OK/FAIL

ROM Firmware integrity OK/FAIL

CR_RAM Integrity of settings in RAM and code that runs in RAM OK/FAIL

Non_Vol Integrity of data stored in nonvolatile memory OK/FAIL

Clock Clock functionality OK/WARN

RTD Integrity of RTD module/communications OK/FAIL

CID_FILE Configured IED description file OK/FAIL

x.x V Power supply status (Refer to Figure 1.3 and Figure 1.4 for examples of

STATUS command responses)

Voltage/FAIL

BATT Clock battery voltage Voltage/WARN

CARD_C Integrity of Card C OK/FAIL

CARD_D Integrity of Card D OK/FAIL

CARD_E Integrity of Card E OK/FAIL

CURRENT Integrity of current board OK/FAIL

DN_MAC_ID Specific DeviceNet card identification Text Data

ASA Manufacturers identifier for DeviceNet Text Data

DN_Rate DeviceNet card network communications data rate ___kbps Text Data

DN_Status DeviceNet connection and fault status 000b bbbb Text Data

Current Offset (IA, IB, IC, IN) DC offset in hardware circuits of current channels OK/WARN

Voltage Offset (VA, VB, VC, VS) DC offset in hardware circuits of voltage channels OK/FAIL

Loading...

Loading...