Chapter 4 INTERFACE SETTINGS

227

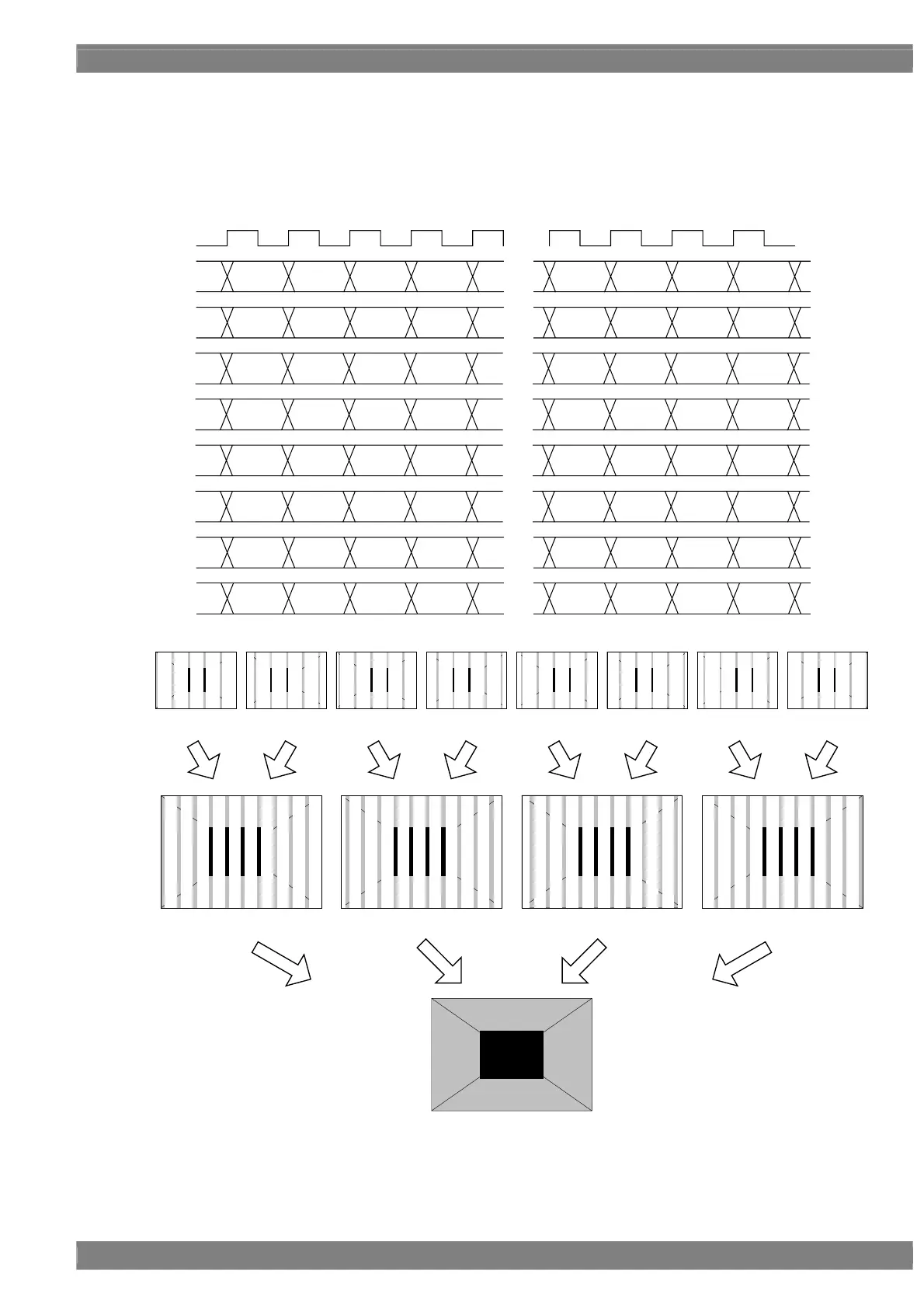

[1] MODE0 (8 Lane ) - No screen splitting

Using 1-8 lanes, the image is output with the pixel assignment as below without splitting.

This example is a case where the resolution is 1920 × 1080, the dot clock frequency is 592 MHz and the output bit

depth is 10 bits.

D 0

D 4

D 8

D 12

・・・

・・・

D 1904

D 1908

D 1912

D 1916

D 3

D 7

D 11

D 15

・・・

D 1907

D 1911

D 1915

D 1919

D 1906

D 1910

D 1914

D 1918

・・・

D 2

D 6

D 10

D 14

D 1

D 5

D 9

D 13

・・・

D 1905

D 1909

D 1913

D 1917

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

・・・

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

・・・

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

・・・

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

・・・

[9:0] [9:0] [9:0] [9:0][9:0] [9:0] [9:0] [9:0]

D 16

D20

D 24

D 28

D 19

D23

D 27

D31

D 18

D22

D26

D 30

D17

D 21

D 25

D 29

D1888

D1892

D1896

D1900

D1891

D1985

D1899

D1903

D1890

D1894

D1898

D1902

D1889

D1983

D1897

D1901

CLK

74MHz

L0~L1079

L0~L1079

L0~L1079

L0~L1079

L0~L1079

L0~L1079

L0~L1079

L0~L1079

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

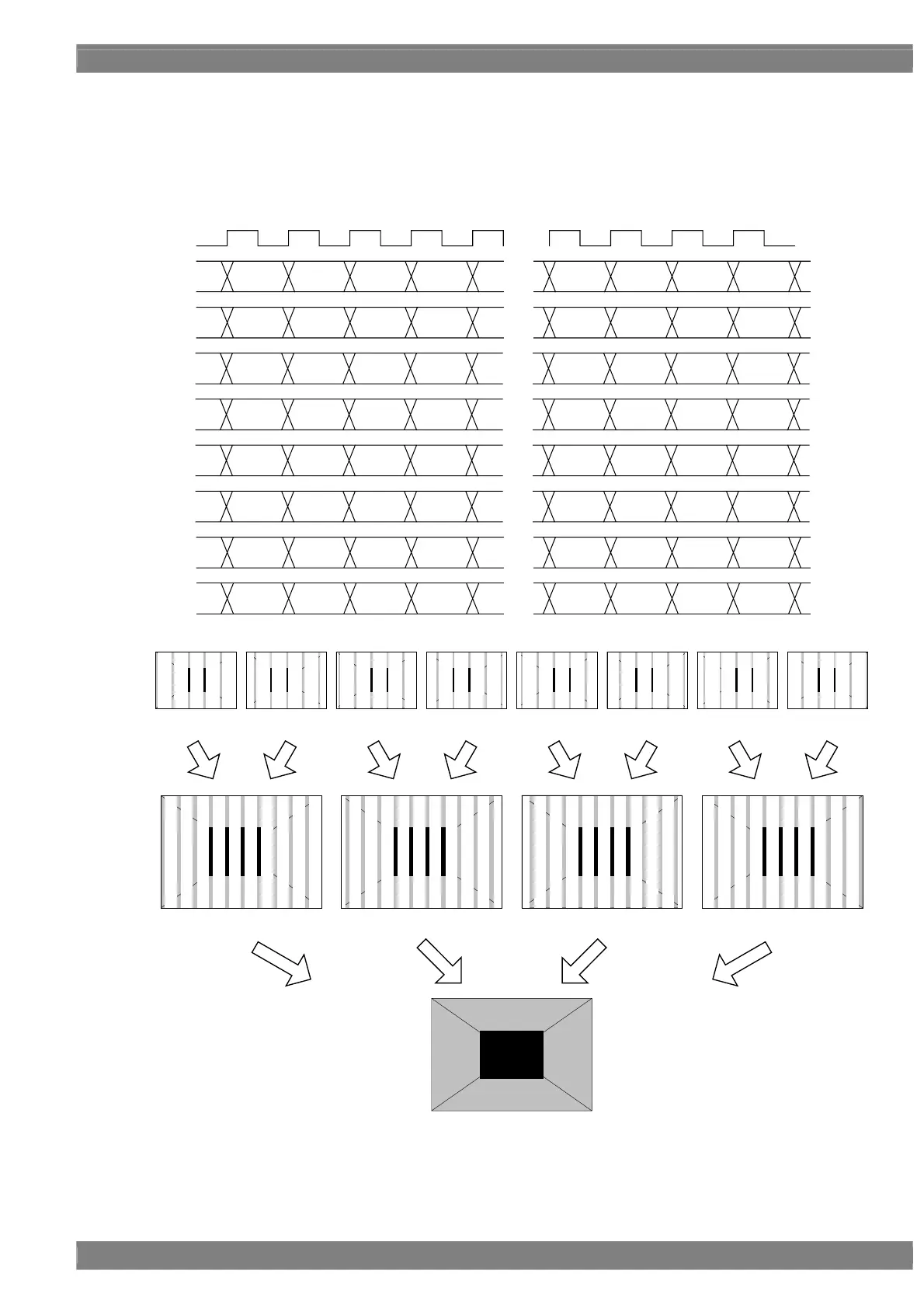

Lane 1 Lane 2 Lane 3

Lane 5-6 Lane 7-8Lane 1-2 Lane 3-4

Lane4 Lane 5 Lane 6 Lane 7 Lane 8

Loading...

Loading...