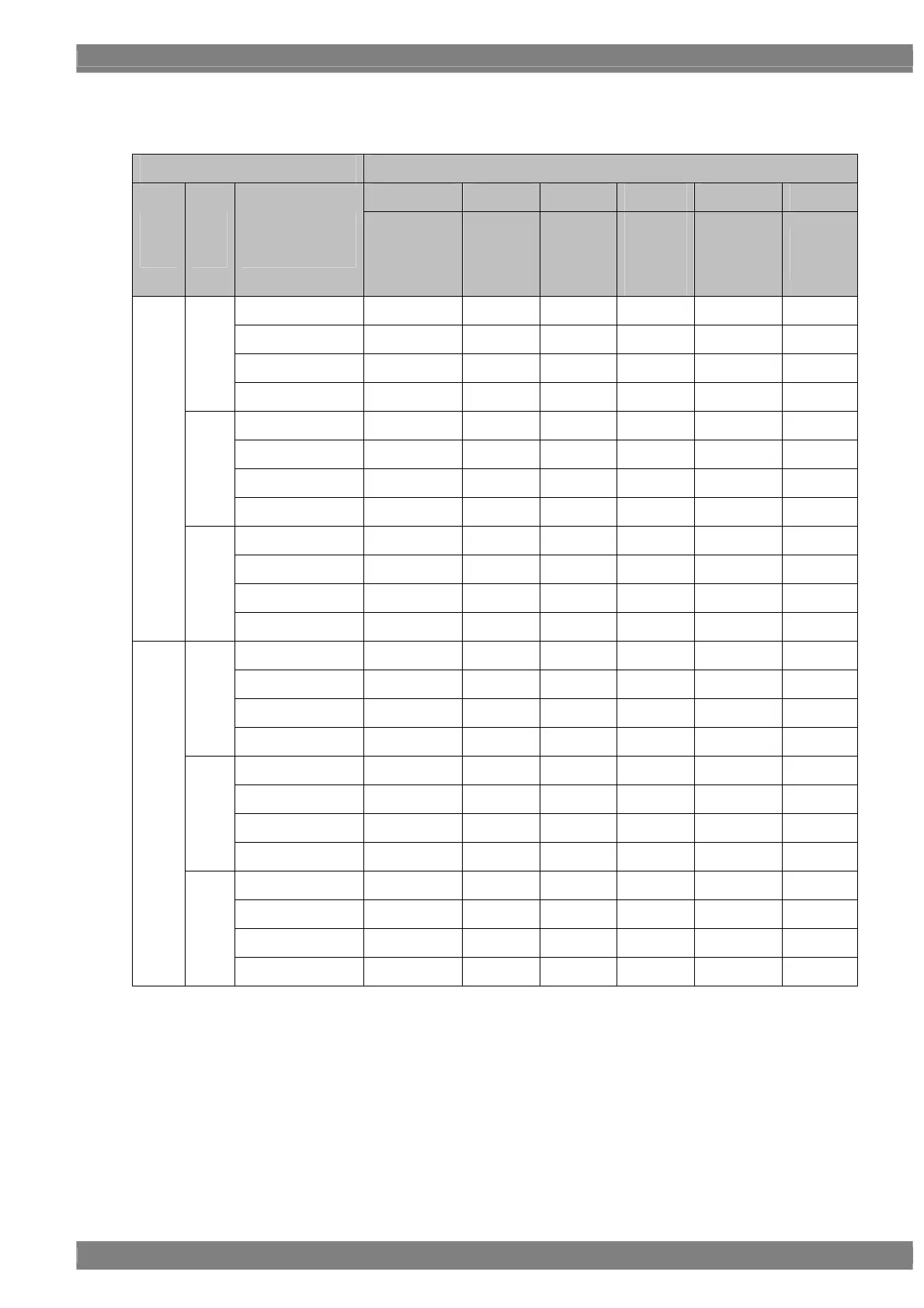

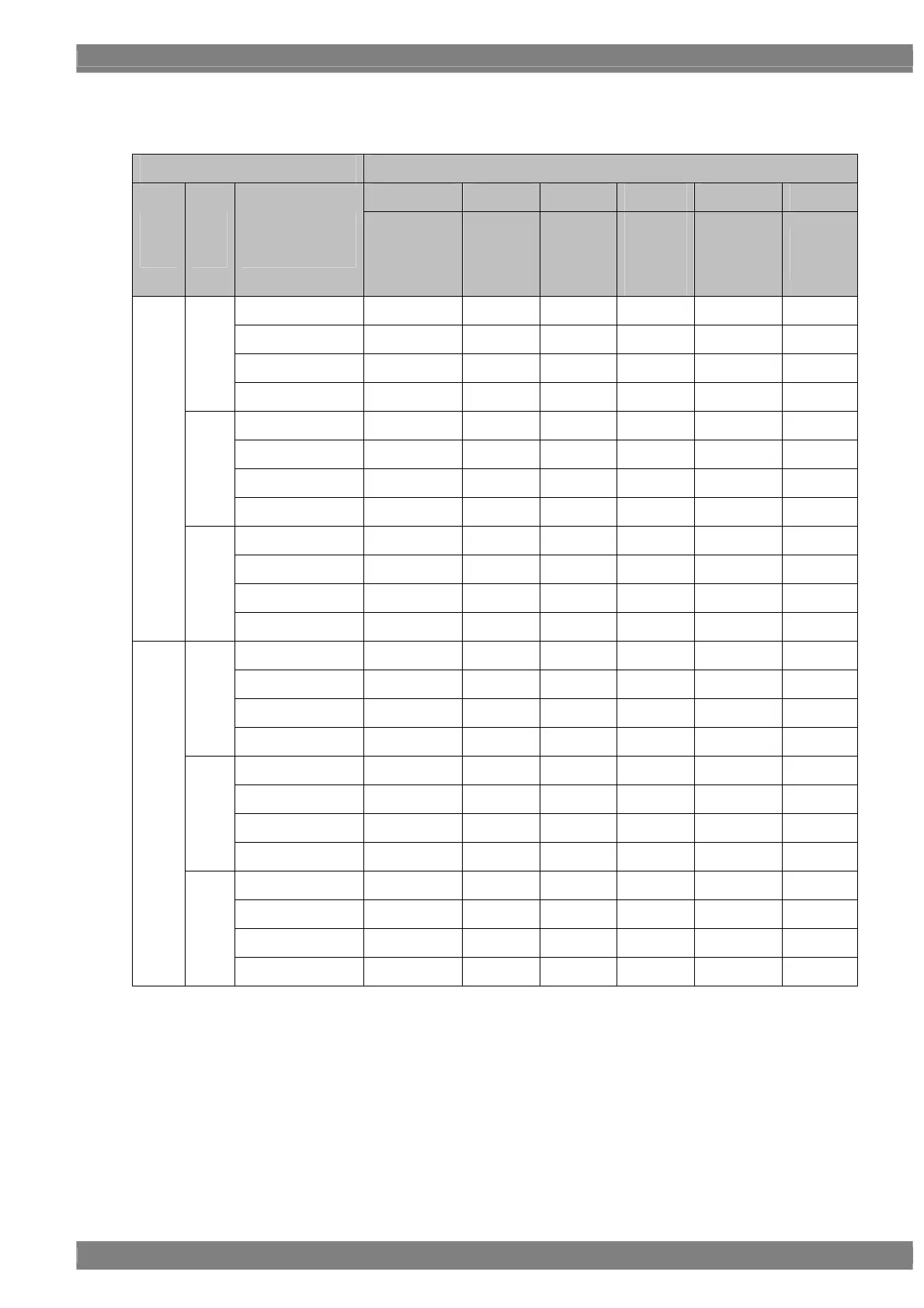

Chapter 11 SPECIFICATIONS

465

*1 The maximum dot clock of DisplayPort changes by the setting of Link Rate, Lane number,

drawing mode, Bit length and color format.

Item Maximum Dot CLK [MHz]

16bit 18bit 20bit 24bit 30bit 16bit

Link

Rate

Lane

count

Drawing

mode

YC422

8bit

RGB

/YC444

6bit

YC422

10bit

RGB

/YC444

8bit

YC422

12bit

YC422

8bit

Single 135 120 108 90 90 135

Dual 270 240 216 180 180 270

Split 540 480 432 360 360 540

1

Split2 1080 960 864 720 720 1080

Single 270 240 216 180 180 270

Dual 340 340 340 340 330 340

Split 660 660 660 660 660 660

2

Split2 1320 1320 1320 1320 1320 1320

Single 330 330 330 330 330 330

Dual 340 340 340 340 330 340

Split 660 660 660 660 660 660

2.7

Gbps

4

Split2 1320 1320 1320 1320 1320 1320

Single 81 72 64.8 54 54 81

Dual 162 144 129.6 108 108 162

Split 324 288 259.2 216 216 324

1

Split2 648 576 518.4 432 432 648

Single 162 144 129.6 108 108 162

Dual 324 288 259.2 216 216 324

Split 648 576 518.4 432 432 648

2

Split2 1296 1152 1036.8 864 864 1296

Single 324 288 259.2 216 216 324

Dual 340 340 340 340 330 340

1.62

Gbps

4

Split 660 660 660 660 660 660

Split2 1320 1320 1320 1320 1320 1320

Loading...

Loading...