RL78/G1H CHAPTER 7 TIMER ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 147 of 920

Dec 22, 2016

The count value can be read by reading timer count register mn (TCRmn).

The count value is set to FFFFH in the following cases.

• When the reset signal is generated

• When the TAUmEN bit of peripheral enable register 0 (PER0) is cleared

• When counting of the slave channel has been completed in the PWM output mode

• When counting of the slave channel has been completed in the delay count mode

The count value is cleared to 0000H in the following cases.

• When the start trigger is input in the capture mode

• When capturing has been completed in the capture mode

Caution The count value is not captured to timer data register mn (TDRmn) even when the TCRmn register

is read.

The TCRmn register read value differs as follows according to operation mode changes and the operating status.

Note This indicates the value read from the TCRmn register when channel n has stopped operating as a timer (TEmn = 0) and

has been enabled to operate as a counter (TSmn = 1). The read value is held in the TCRmn register until the count

operation starts.

Remark m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3)

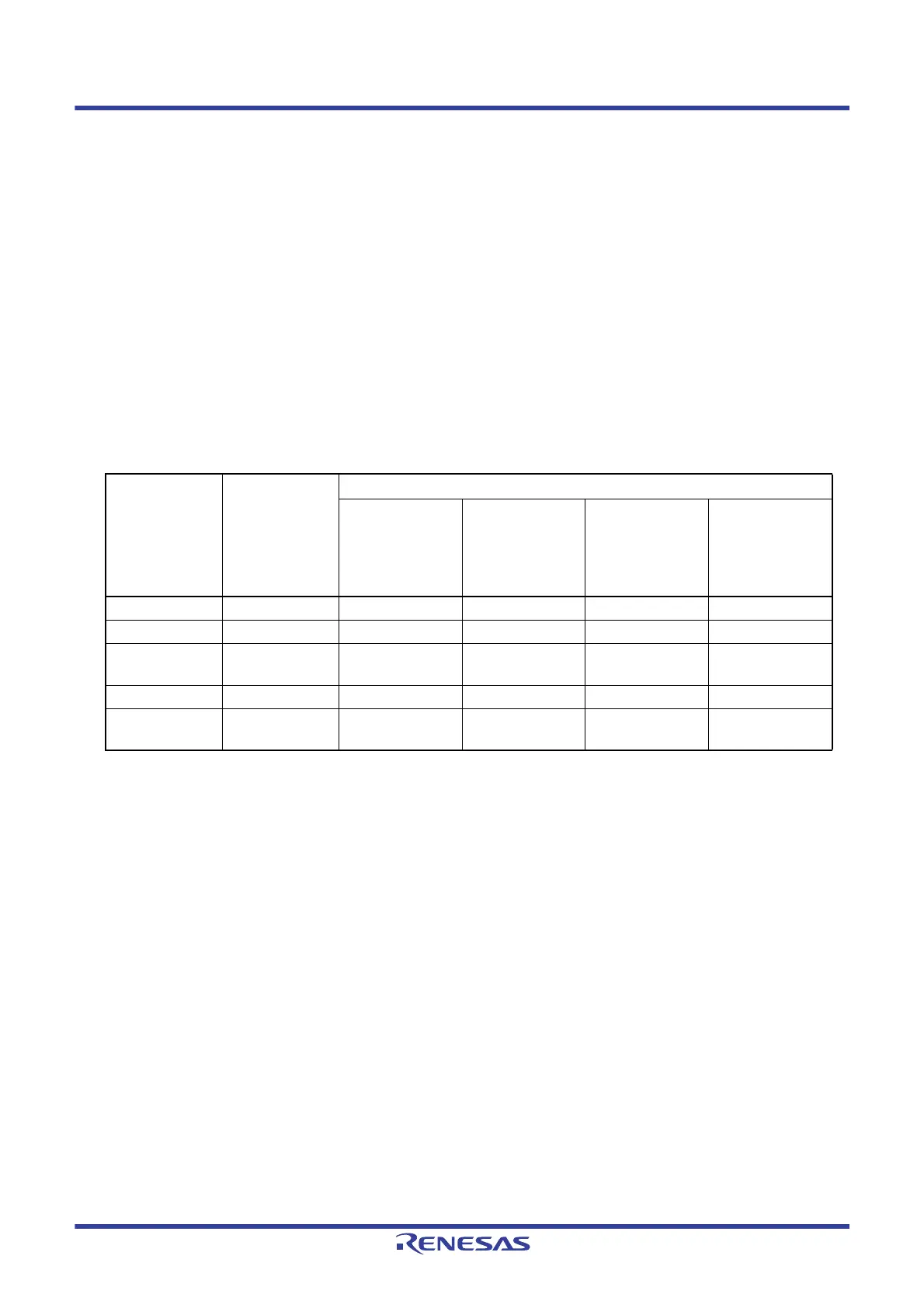

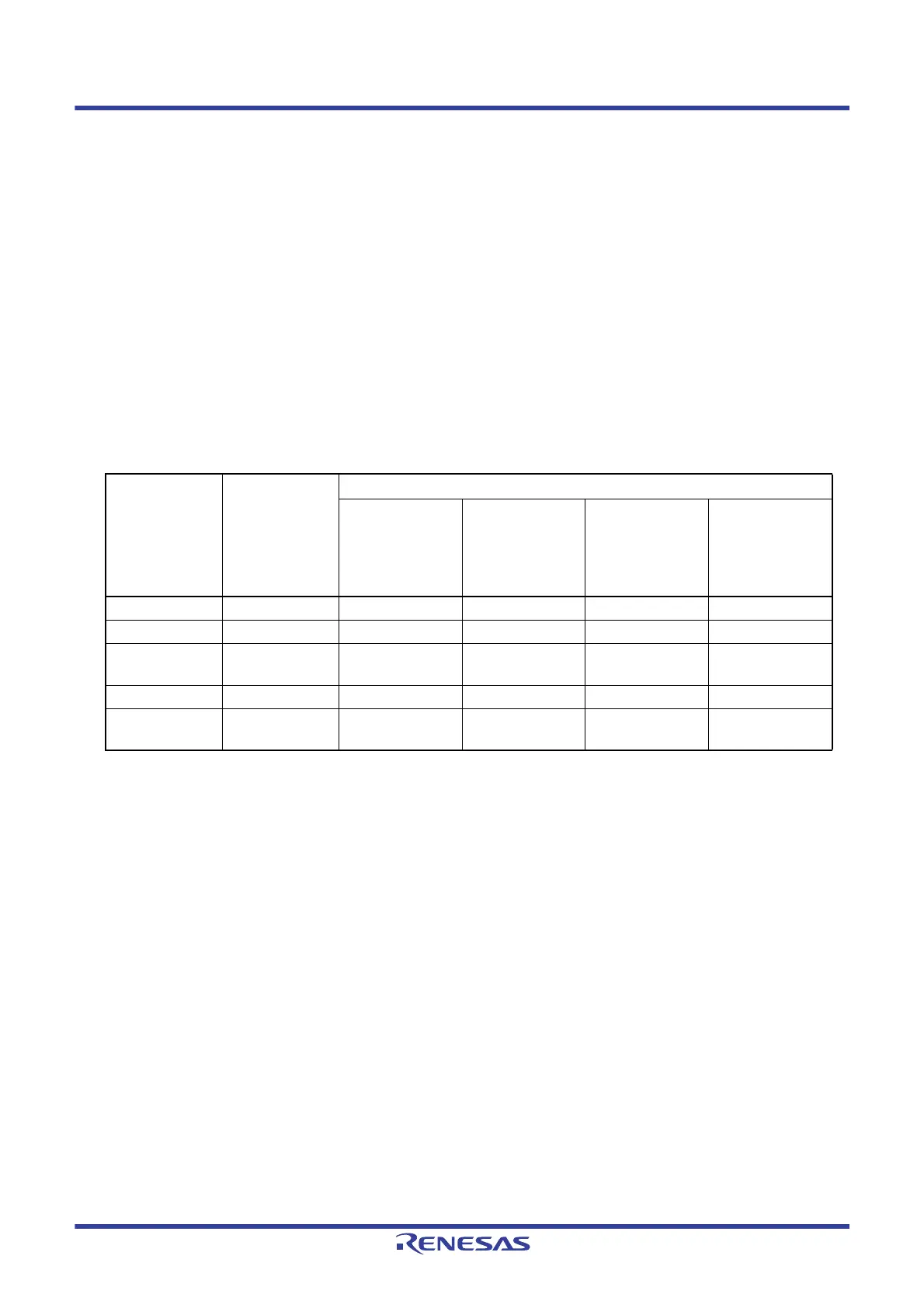

Table 7 - 2 Timer Count Register mn (TCRmn) Read Value in Various Operation Modes

Operation Mode Count Mode

Timer count register mn (TCRmn) Read Value

Note

Value if the

operation mode was

changed after

releasing reset

Value if the

Operation was

restarted after count

operation paused

(TTmn = 1)

Value if the

operation mode was

changed after count

operation paused

(TTmn = 1)

Value when waiting

for a start trigger

after one count

Interval timer mode Count down FFFFH Value if stop Undefined —

Capture mode Count up 0000H Value if stop Undefined —

Event counter

mode

Count down FFFFH Value if stop Undefined —

One-count mode Count down FFFFH Value if stop Undefined FFFFH

Capture & one-

count mode

Count up 0000H Value if stop Undefined Capture value of

TDRmn register + 1

Loading...

Loading...