RL78/G1H CHAPTER 7 TIMER ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 153 of 920

Dec 22, 2016

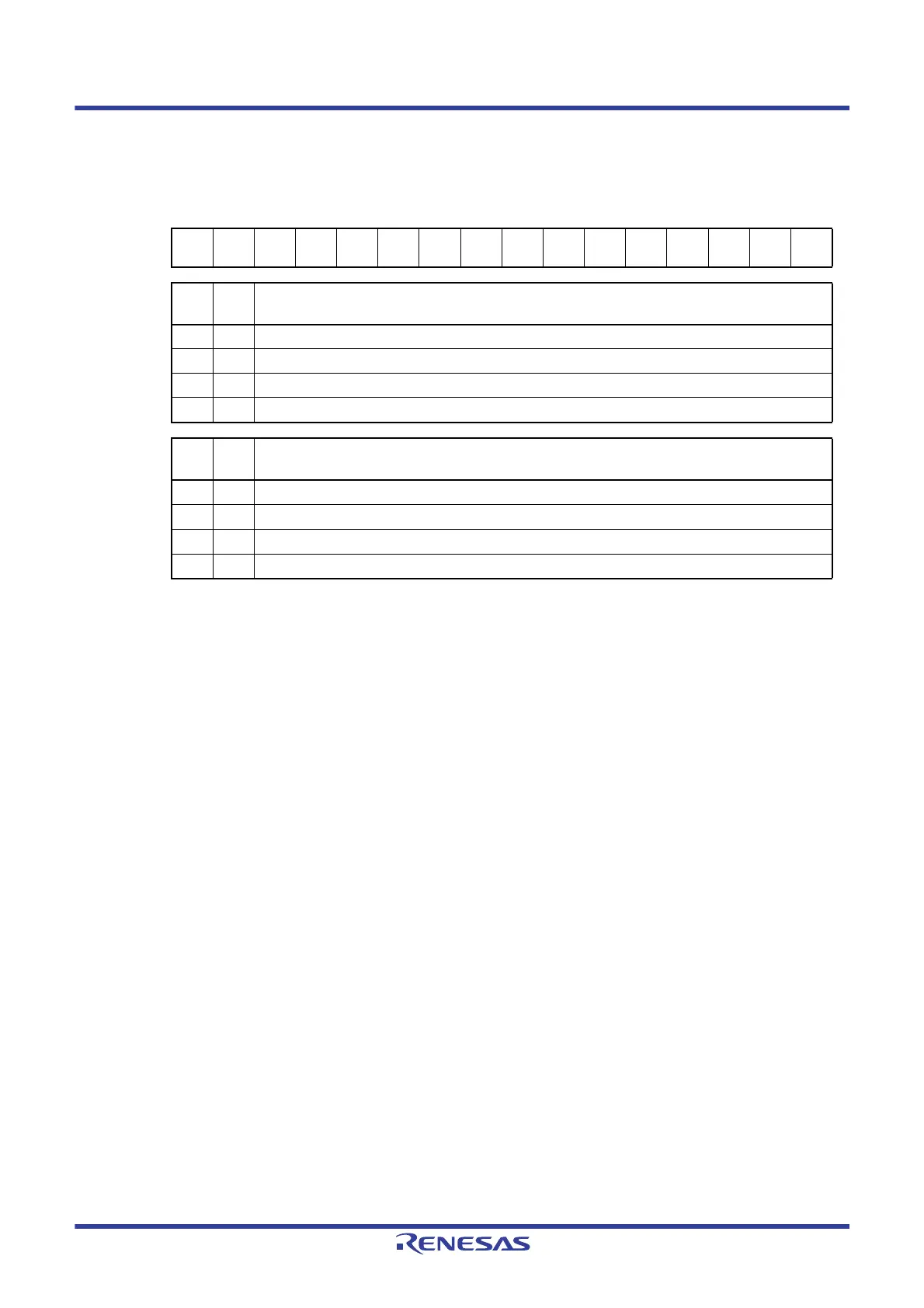

Figure 7 - 11 Format of Timer clock select register m (TPSm) (2/2)

Note When changing the clock selected for fCLK (by changing the system clock control register (CKC) value), stop

timer array unit (TTm = 000FH).

The timer array unit must also be stopped if the operating clock (f

MCK) or the valid edge of the signal input

from the TImn pin is selected.

Caution Be sure to clear bits 15, 14, 11, 10 to “0”.

Remark 1.

fCLK: CPU/peripheral hardware clock frequency

Remark 2. For details of a signal of fCLK/2

r

selected with the TPSm register, see 7.5.1 Count clock (fTCLK).

Address: F01B6H, F01B7H (TPS0), F01F6H, F01F7H (TPS1) After reset: 0000H R/W

Symbol1514131211109876543210

TPSm 0 0

PRSm

31

PRSm

30

00

PRSm

21

PRSm

20

PRSm

13

PRSm

12

PRSm

11

PRSm

10

PRSm

03

PRSm

02

PRSm

01

PRSm

00

PRS

m21

PRS

m20

Selection of operation clock (CKm2)

Note

00fCLK/2

01

f

CLK/2

2

10

f

CLK/2

4

11

f

CLK/2

6

PRS

m31

PRS

m30

Selection of operation clock (CKm3)

Note

00

f

CLK/2

8

01

f

CLK/2

10

10

f

CLK/2

12

11

f

CLK/2

14

Loading...

Loading...