RL78/G1H CHAPTER 7 TIMER ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 155 of 920

Dec 22, 2016

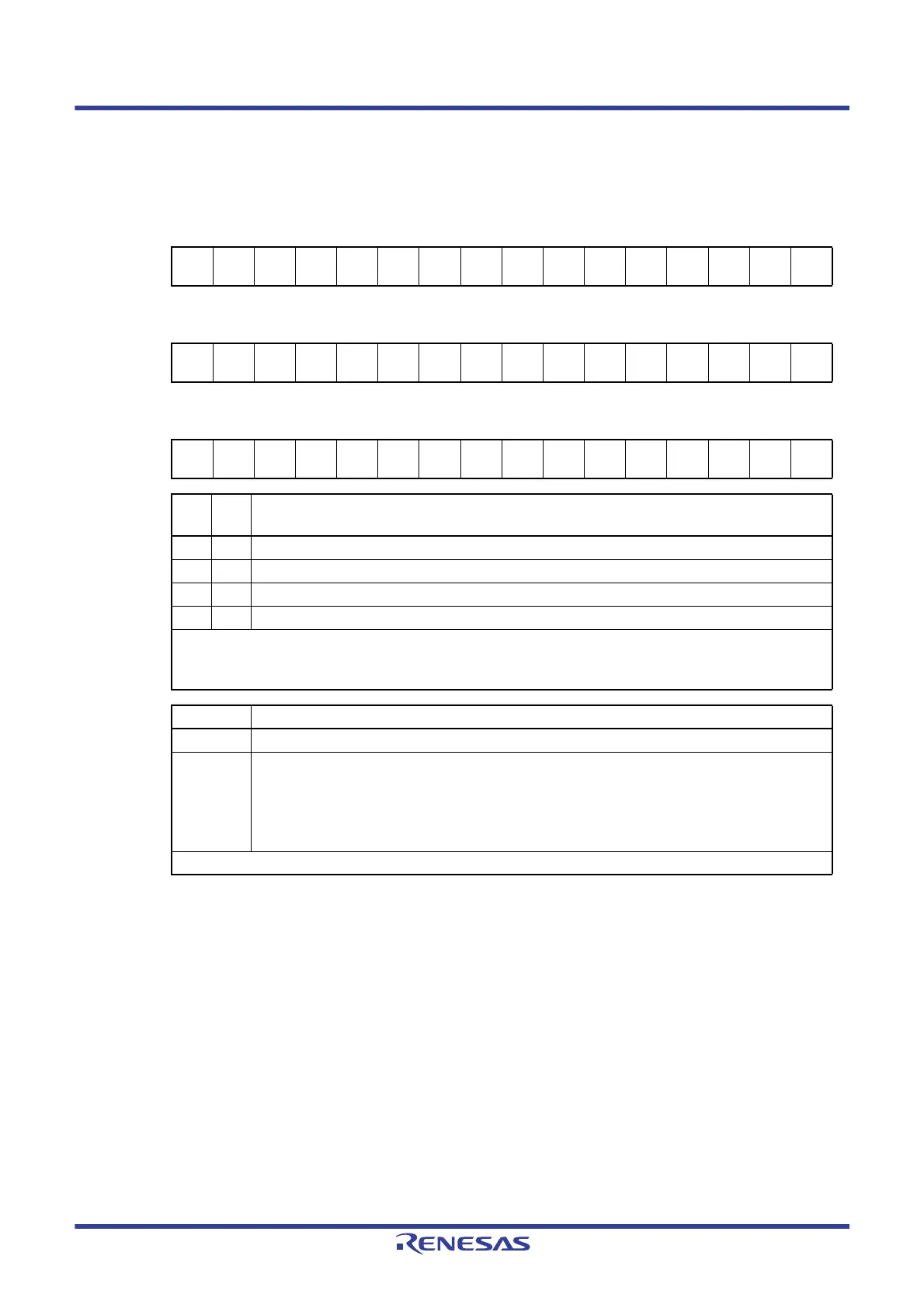

Figure 7 - 12 Format of Timer mode register mn (TMRmn) (1/4)

Note Bit 11 is fixed at 0 of read only, write is ignored.

Caution 1. Be sure to clear bits 13, 5, and 4 to “0”.

Caution 2. The timer array unit must be stopped (TTm = 00FFH) if the clock selected for f

CLK is changed (by

changing the value of the system clock control register (CKC)), even if the operating clock specified

by using the CKSmn0 and CKSmn1 bits (f

MCK) or the valid edge of the signal input from the TImn pin

is selected as the count clock (f

TCLK).

Remark

m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3)

Address: F0190H, F0191H (TMR00) to F0196H, F0197H (TMR03), After reset: 0000H R/W

F01D0H, F01D1H (TMR10) to F01D6H, F01D7H (TMR13)

Symbol1514131211109876543210

TMRmn

(n = 2)

CKS

mn1

CKS

mn0

0

CCS

mn

MAST

ERmn

STS

mn2

STS

mn1

STS

mn0

CIS

mn1

CIS

mn0

00

MD

mn3

MD

mn2

MD

mn1

MD

mn0

Symbol1514131211109876543210

TMRmn

(n = 1, 3)

CKS

mn1

CKS

mn0

0

CCS

mn

SPLIT

mn

STS

mn2

STS

mn1

STS

mn0

CIS

mn1

CIS

mn0

00

MD

mn3

MD

mn2

MD

mn1

MD

mn0

Symbol1514131211109876543210

TMRmn

(n = 0)

CKS

mn1

CKS

mn0

0

CCS

mn

0

Note

STS

mn2

STS

mn1

STS

mn0

CIS

mn1

CIS

mn0

00

MD

mn3

MD

mn2

MD

mn1

MD

mn0

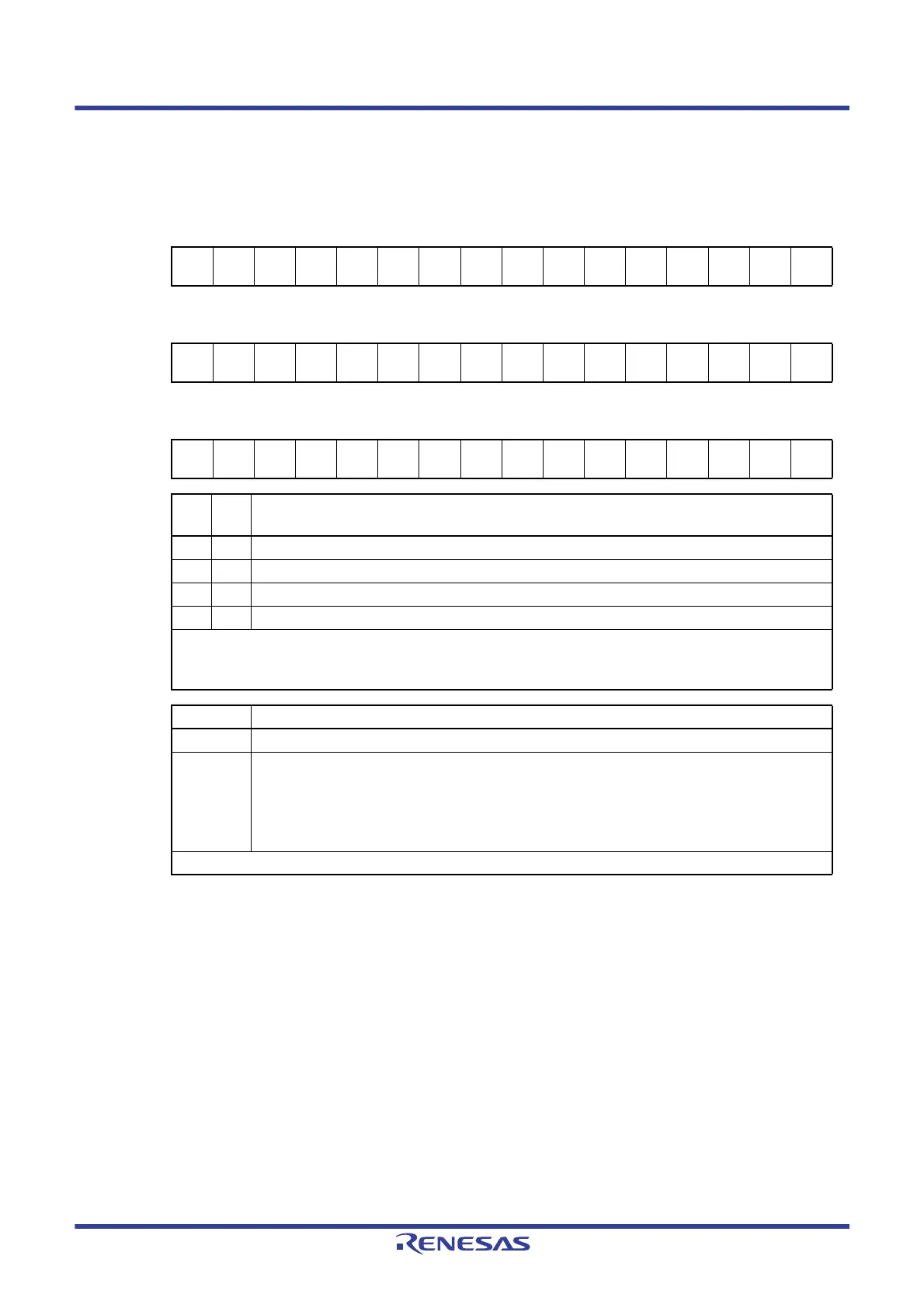

CKS

mn1

CKS

mn0

Selection of operation clock (f

MCK) of channel n

0 0 Operation clock CKm0 set by timer clock select register m (TPSm)

0 1 Operation clock CKm2 set by timer clock select register m (TPSm)

1 0 Operation clock CKm1 set by timer clock select register m (TPSm)

1 1 Operation clock CKm3 set by timer clock select register m (TPSm)

Operation clock (f

MCK) is used by the edge detector. A count clock (fTCLK) and a sampling clock are generated

depending on the setting of the CCSmn bit.

The operation clocks CKm2 and CKm3 can only be selected for channels 1 and 3.

CCSmn Selection of count clock (f

TCLK) of channel n

0 Operation clock (f

MCK) specified by the CKSmn0 and CKSmn1 bits

1 Valid edge of input signal input from the TImn pin

• For unit 0

For channel 0, valid edge of input signal selected by TIS0

For channel 1, valid edge of input signal selected by TIS0

For channel 3, valid edge of input signal selected by TI03

Count clock (f

TCLK) is used for the counter, output controller, and interrupt controller.

Loading...

Loading...