RL78/G1H CHAPTER 16 DATA TRANSFER CONTROLLER (DTC)

R01UH0575EJ0120 Rev. 1.20 Page 528 of 920

Dec 22, 2016

Caution For the bits to which no function is assigned, be sure to set their values to 0.

Remark

i = 0 to 4

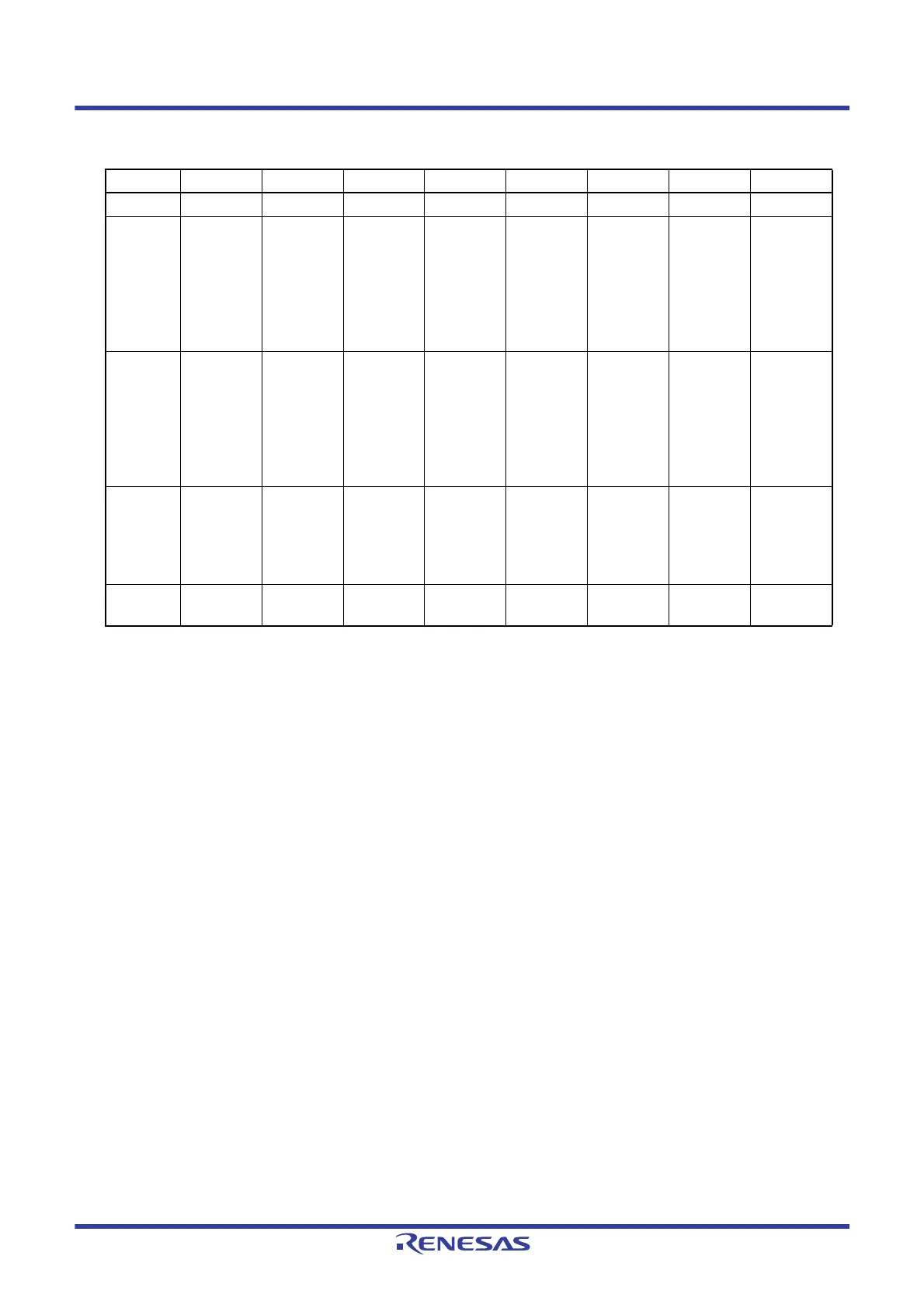

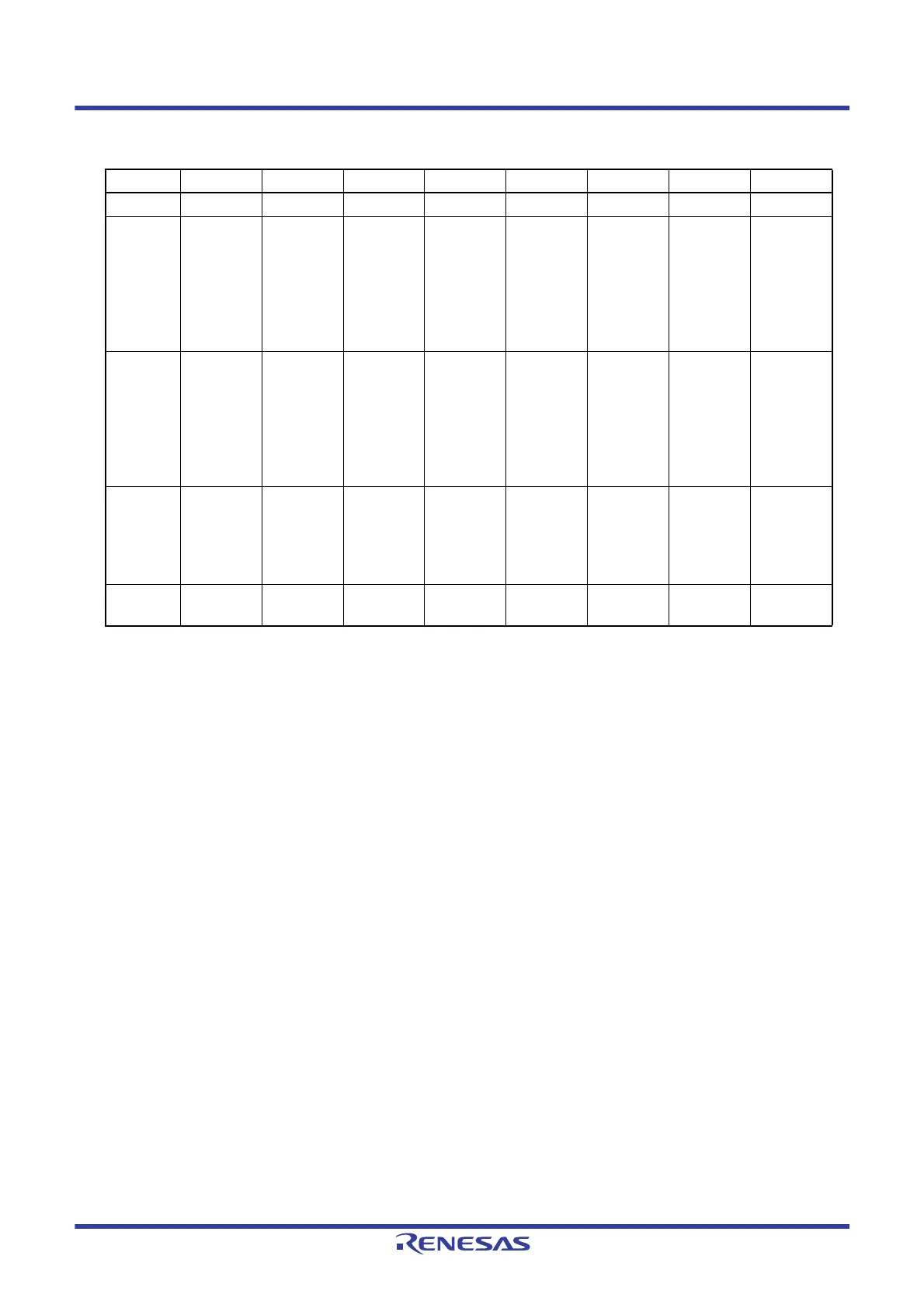

Table 16 - 6 Correspondences between Interrupt Sources and Bits DTCENi0 to DTCENi7

Register DTCENi7 Bit DTCENi6 Bit DTCENi5 Bit DTCENi4 Bit DTCENi3 Bit DTCENi2 Bit DTCENi1 Bit DTCENi0 Bit

DTCEN0 Reserved INTP0 Reserved Reserved INTP3 INTP4 Reserved INTP6

DTCEN1 INTP7 Reserved A/D

conversion

end

Reserved Reserved UART1

reception

transfer end

UART1

transmission

transfer

end/CSI10

transfer end

or buffer

empty

CSI21

transfer end

or buffer

empty

DTCEN2 CSI20

transfer end

or buffer

empty

UART3

reception

transfer end

UART3

transmission

transfer

end/CSI30

transfer end

or buffer

empty

End of

channel 0 of

timer array

unit 0 count

or capture

End of

channel 1 of

timer array

unit 0 count

or capture

End of

channel 2 of

timer array

unit 0 count

or capture

End of

channel 3 of

timer array

unit 0 count

or capture

End of

channel 0 of

timer array

unit 1 count

or capture

DTCEN3 End of

channel 1 of

timer array

unit 1 count

or capture

End of

channel 2 of

timer array

unit 1 count

or capture

End of

channel 3 of

timer array

unit 1 count

or capture

Reserved Reserved Reserved Reserved Reserved

DTCEN4 Reserved Reserved Reserved Reserved Reserved Timer RJ0

underflow

Reserved Reserved

Loading...

Loading...