RL78/G1H CHAPTER 18 RF TRANSCEIVER

R01UH0575EJ0120 Rev. 1.20 Page 628 of 920

Dec 22, 2016

(62) PHY header receive register (BBPHRRX)

This register is used to store the PHY header receive data.

The values of bits 0 to 2, FCSTYPE, and Data Whitening of the PHY header data when receiving the non-

mode switch frame are stored. The timing of the storage is the same as the timing when the frame length

value is stored.

The reading value is corresponding save bank specified by receive data save bank select bit.

The BBPHRRX register is read by the serial interface in 8-bit units.

Reset signal generation clears this register to 00H.

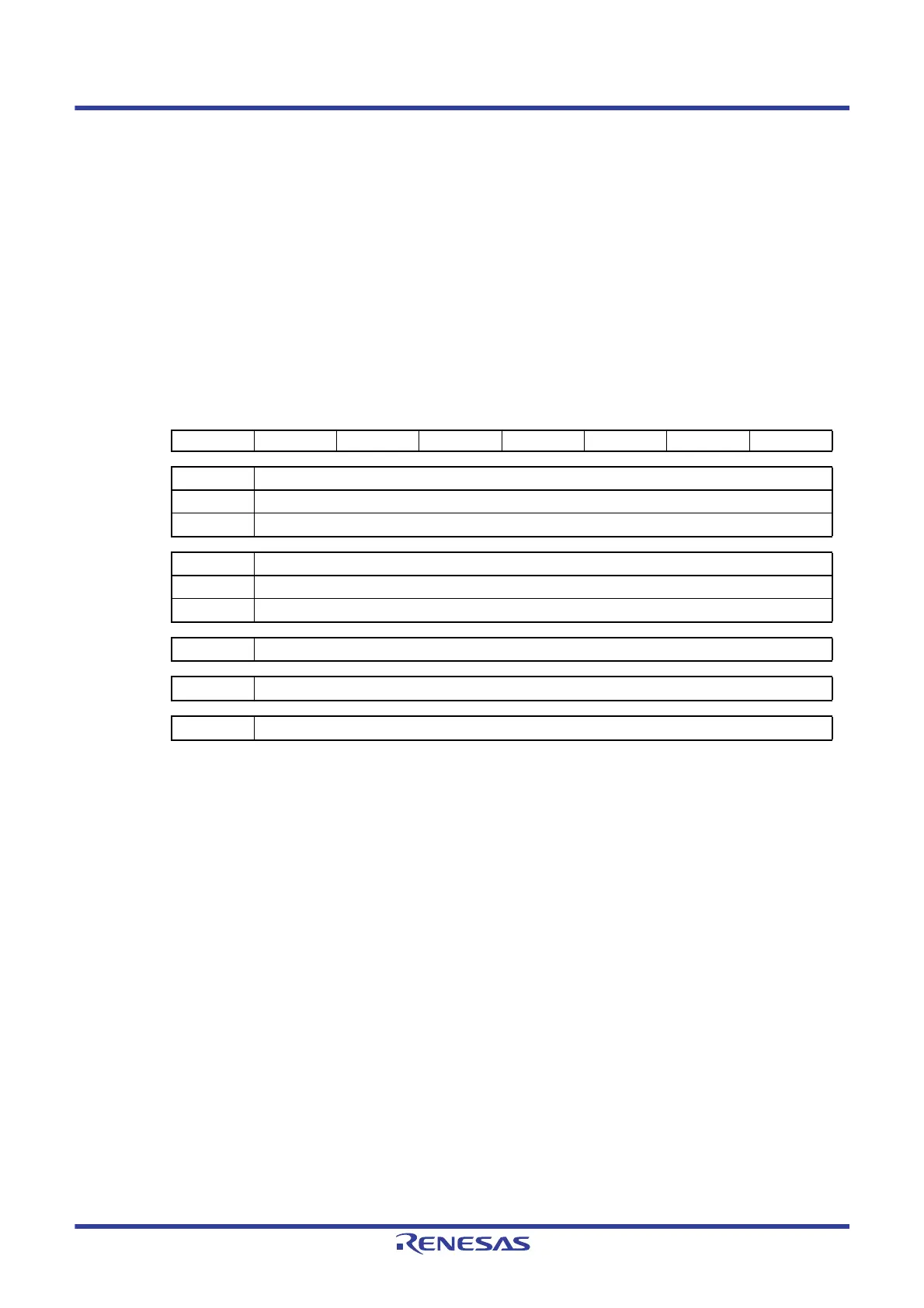

Figure 18 - 75 PHY Header Receive Register (BBPHRRX) Format

Address:

00BEH

After reset: 00H R

Symbol76543210

BBPHRRX

0 0 0 DWBIT FCSTYPE PHRRX2 PHRRX1 PHRRX0

DWBIT Data whitening bit

0 Disable

1 Enable

FCSTYPE FCS type bit

0 32 bits

1 16 bits

PHRRX2 PHR receive bit 2 value

PHRRX1 PHR receive bit 1 value

PHRRX0 PHR receive bit 0 value

Loading...

Loading...