RL78/G1H CHAPTER 22 POWER-ON-RESET CIRCUIT

R01UH0575EJ0120 Rev. 1.20 Page 757 of 920

Dec 22, 2016

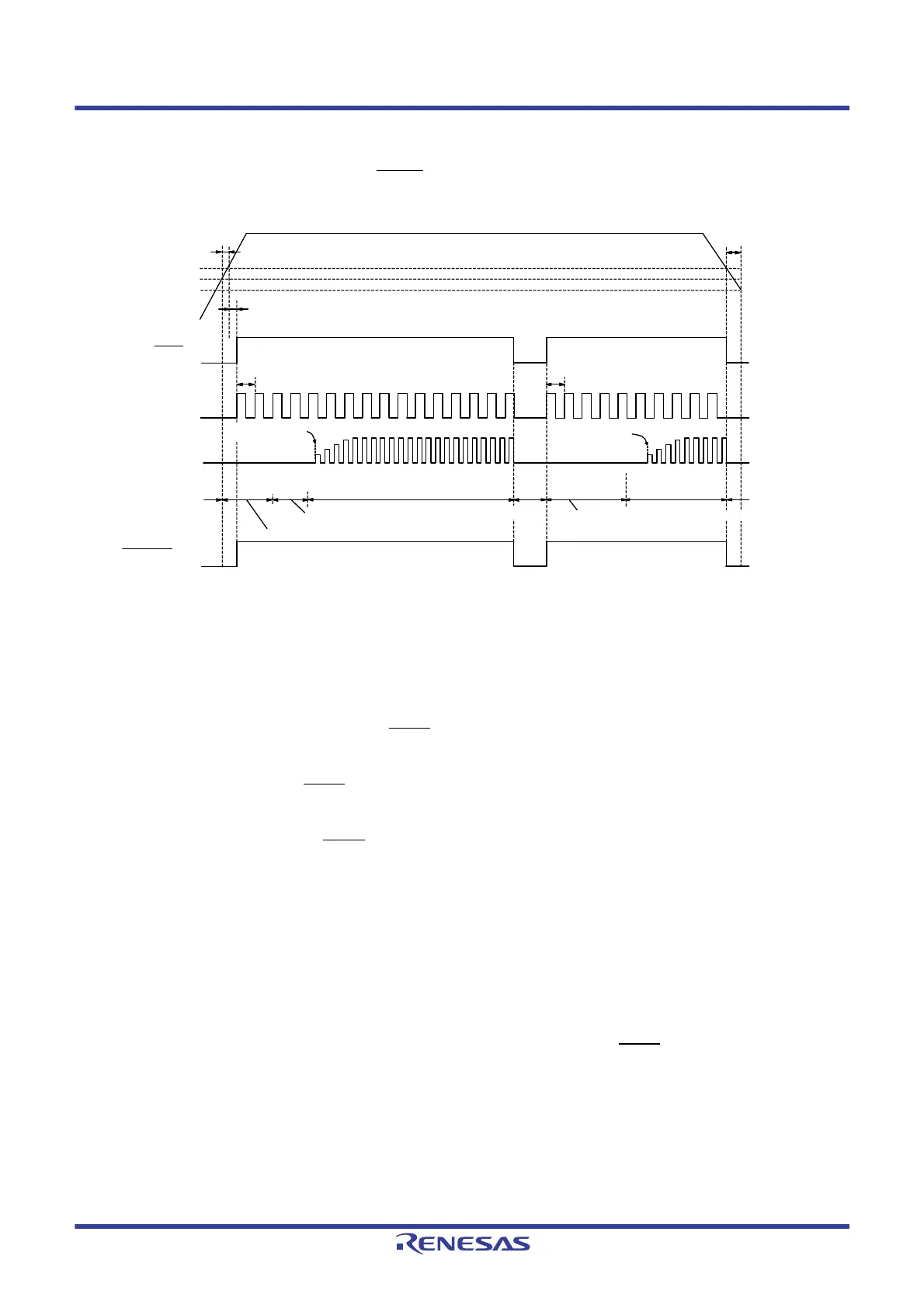

Figure 22 - 2 Timing of Generation of Internal Reset Signal by Power-on-reset Circuit and Voltage Detector (1/3)

(1) When using an external reset by the RESET pin

Note 1. The internal reset processing time includes the oscillation accuracy stabilization time of the high-speed on-chip oscillator

clock.

Note 2. The high-speed on-chip oscillator clock and a high-speed system clock or subsystem clock can be selected as the CPU

clock. To use the X1 clock, use the oscillation stabilization time counter status register (OSTC) to confirm the lapse of the

oscillation stabilization time. To use the XT1 clock, use the timer function for confirmation of the lapse of the stabilization

time.

Note 3. The time until normal operation starts includes the following reset processing time when the external reset is released

(after the first release of POR) after the RESET

signal is driven high (1) as well as the voltage stabilization wait time after

V

POR (1.51 V, TYP.) is reached.

Reset processing time when the external reset is released is shown below.

After the first release of RESET

following POR: 0.672 ms (TYP.), 0.832 ms (MAX.) (when the LVD is in use)

0.399 ms (TYP.), 0.519 ms (MAX.) (when the LVD is off)

Note 4. Reset processing time when the external reset is released after the second release of POR is shown below.

After the second release of RESET

following POR: 0.531 ms (TYP.), 0.675 ms (MAX.) (when the LVD is in use)

0.259 ms (TYP.), 0.362 ms (MAX.) (when the LVD is off)

Note 5. After power is supplied, the reset state must be retained until the operating voltage becomes in the range defined in 31.4

AC Characteristics. This is done by controlling the externally input reset signal.

After power supply is turned off, this LSI should be placed in the STOP mode, or in the reset state by utilizing the voltage

detection circuit or externally input reset signal, before the voltage falls below the operating range. When restarting the

operation, make sure that the operation voltage has returned within the range of operation.

Remark V

POR: POR power supply rise detection voltage

V

PDR: POR power supply fall detection voltage

Caution For power-on reset, be sure to use the externally input reset signal on the RESET

pin when the LVD is off. For

details, see CHAPTER 23 VOLTAGE DETECTOR.

Supply voltage

(V

DD)

V

POR = 1.51 V (TYP.)

V

PDR = 1.50 V (TYP.)

Operating voltage

range lower limit

0 V

RESET pin

10 µs or more

Internal reset signal

Normal operation

Note 2

(high-speed on-chip oscillator clock)

Wait for oscillation accuracy stabilization

Note 1

Reset

period

(oscillation

stop)

Normal operation

Note 2

(high-speed on-chip

oscillator clock)

Operation stops

Reset processing time when an external reset is released

Note 3

Voltage stabilization wait time: 0.99 ms (TYP.), 2.30 ms (MAX)

Reset processing time when an external reset is released

Note 3

High-speed on-chip

oscillator clock (f

IH)

High-speed

system clock (f

MX)

(when X1 oscillation

is selected)

Operation

stops

CPU

Wait for oscillation accuracy stabilization

Note 1

Starting oscillation is

specified by software

Starting oscillation is

specified by software

Note 5

Note 5

Loading...

Loading...