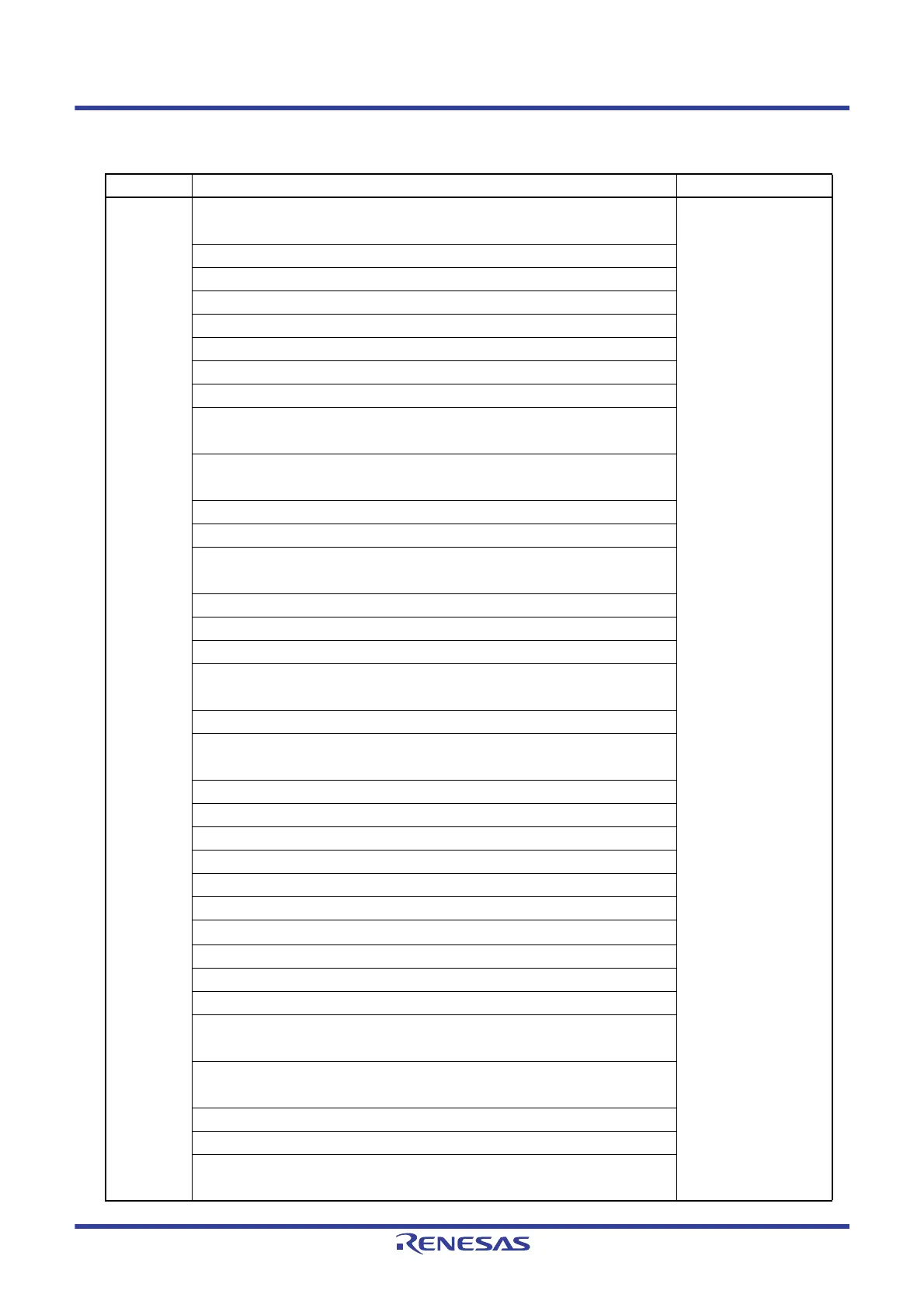

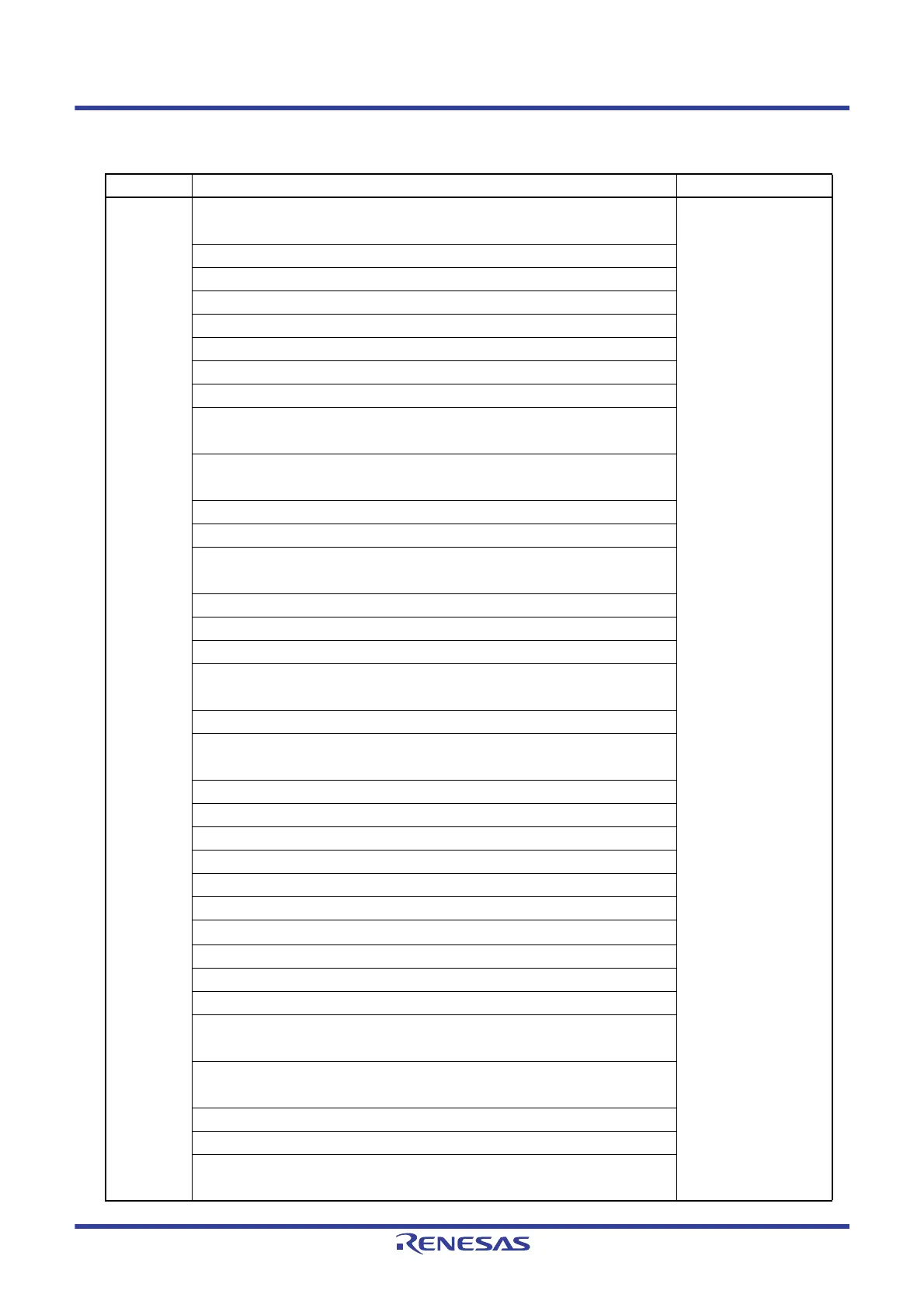

RL78/G1H APPENDIX A REVISION HISTORY

R01UH0575EJ0120 Rev. 1.20 Page 914 of 920

Dec 22, 2016

(3/9)

Edition Description Chapter

Rev1.00 Change of description in 18.4.4 (60) Mode switch frame receive register

(BBRXMODESW)

CHAPTER 18 RF

TRANSCEIVER

Change of description in 18.4.4 (61) Transmit data counter register (BBTXCOUNT)

Change of description in 18.4.4 (62) PHY header receive register (BBPHRRX)

Change of description in 18.4.4 (63) Preamble setting register (BBPABL)

Change of description in 18.4.4 (64) SFD setting register (BBSFD)

Change of description in 18.4.4 (66) ANT0 read register (BBANT0RD)

Change of description in 18.4.4 (67) ANT1 read register (BBANT1RD)

Change of description in 18.4.4 (68) Antenna switch time register (BBANTDIVTIM)

Change of description in 18.4.4 (69) Receive start timeout setting register

(BBANTTIMOUT)

Change of description in 18.4.4 (71) Back off period total number register

(BBBOPTOTAL)

Change of description in 18.4.4 (72) CCA total number register (BBCCATOTAL)

Deletion of 18.4.4 (72) RF initial setting register (RFINI)

Change of description in 18.4.4 (73) RF initial setting register 00 to 02 (RFINI00 to

RFINI02)

Addition of 18.4.4 (74) RF initial setting register 10 to 12 (RFINI10 to RFINI12)

Change of description in 18.4.4 (75) PAN identifier register 1 (BBPANID1)

Change of description in 18.4.4 (76) Short address register 1 (BBSHORTAD1)

Change of description in 18.4.4 (77) Extended address register 1 (BBEXTENDAD10 to

BBEXTENDAD13)

Change of description in 18.4.4 (78) Receive timeout register (BBTIMEOUT)

Deletion of in 18.4.4 (77) Transmit CP current select register 1 (TXCPISL1) to 18.4.4

(80) Transmit capacitance and resistance select register 1 (TXCR1)

Change of description in 18.4.4 (79) ANTSW control register (ANTSWCON)

Change of description in 18.4.4 (80) Clock output control register (CLKOUTCON)

Change of description in 18.4.4 (81) Port direction register (GPIODIR)

Change of description in 18.4.4 (82) Port data register (GPIODATA)

Deletion of in 18.4.4 (85) Upon-transmission power supply setting register 0 (TXCON0)

Change of description in 18.4.4 (83) SFD setting register 2 (BBSFD2)

Change of description in 18.4.4 (84)

SFD setting register 3 (BBSFD3)

Change of description in 18.4.4 (85) SFD setting register 4 (BBSFD4)

Addition of description to 18.4.4 (86) FEC control register (BBFECCON)

Addition of Caution to Figure 18 - 99 FEC Control Register (BBFECCON) Format

Addition of description to 18.4.3 (87) Address filter extension address control register

(BBADFCON)

Change of Figure 18 - 100 Address Filter Extension Address Control Register

(BBADFCON) Format

Addition of description to 18.4.4 (88) Antenna diversity mode register 2 (BBANTDIV2)

Change of Figure 18 - 101 Antenna Diversity Mode Register 2 (BBANTDIV2) Format

Addition of 18.4.4 (89) Lower limit threshold setting register after SFD detection

(PWRLOWTH2)

Loading...

Loading...