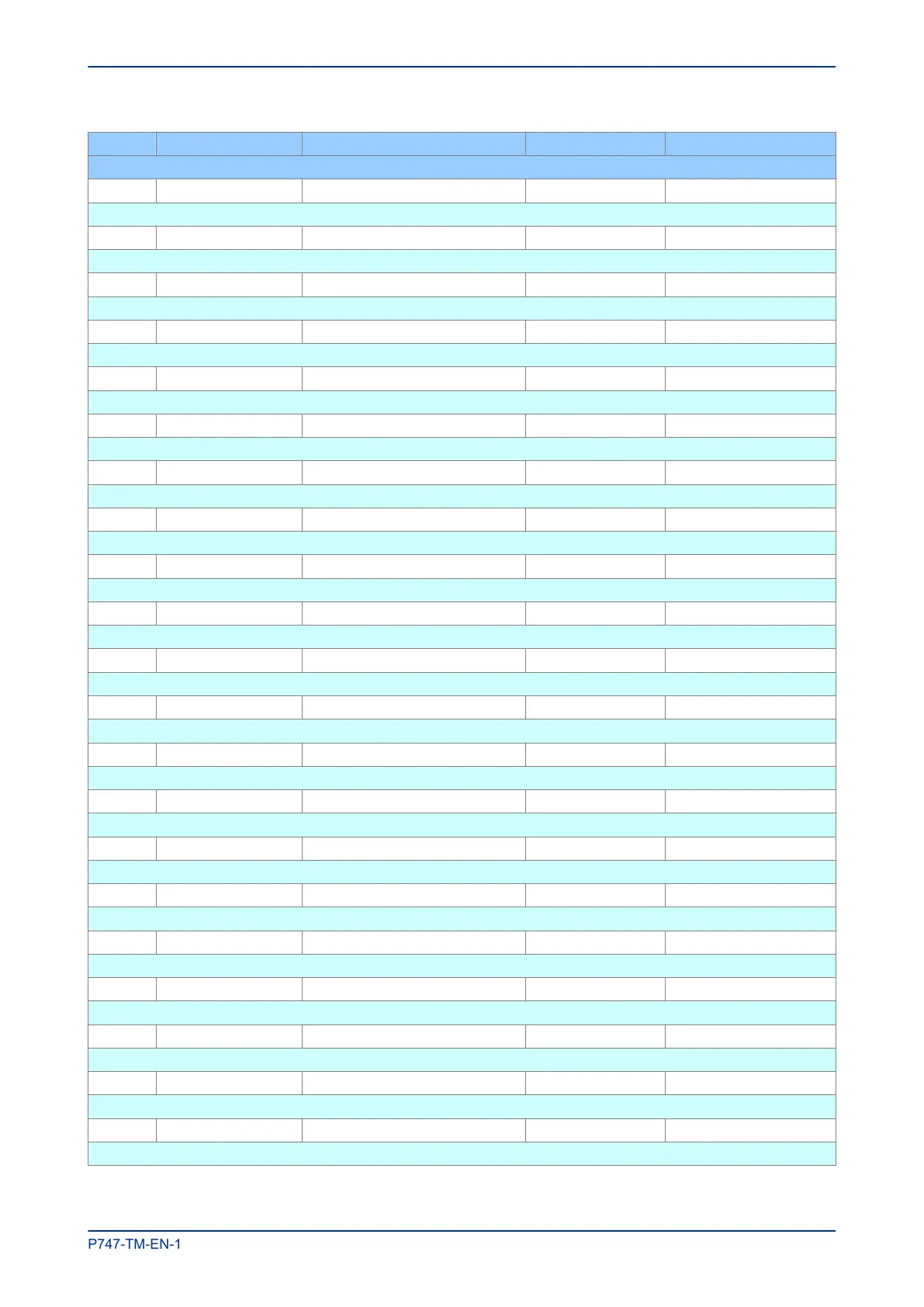

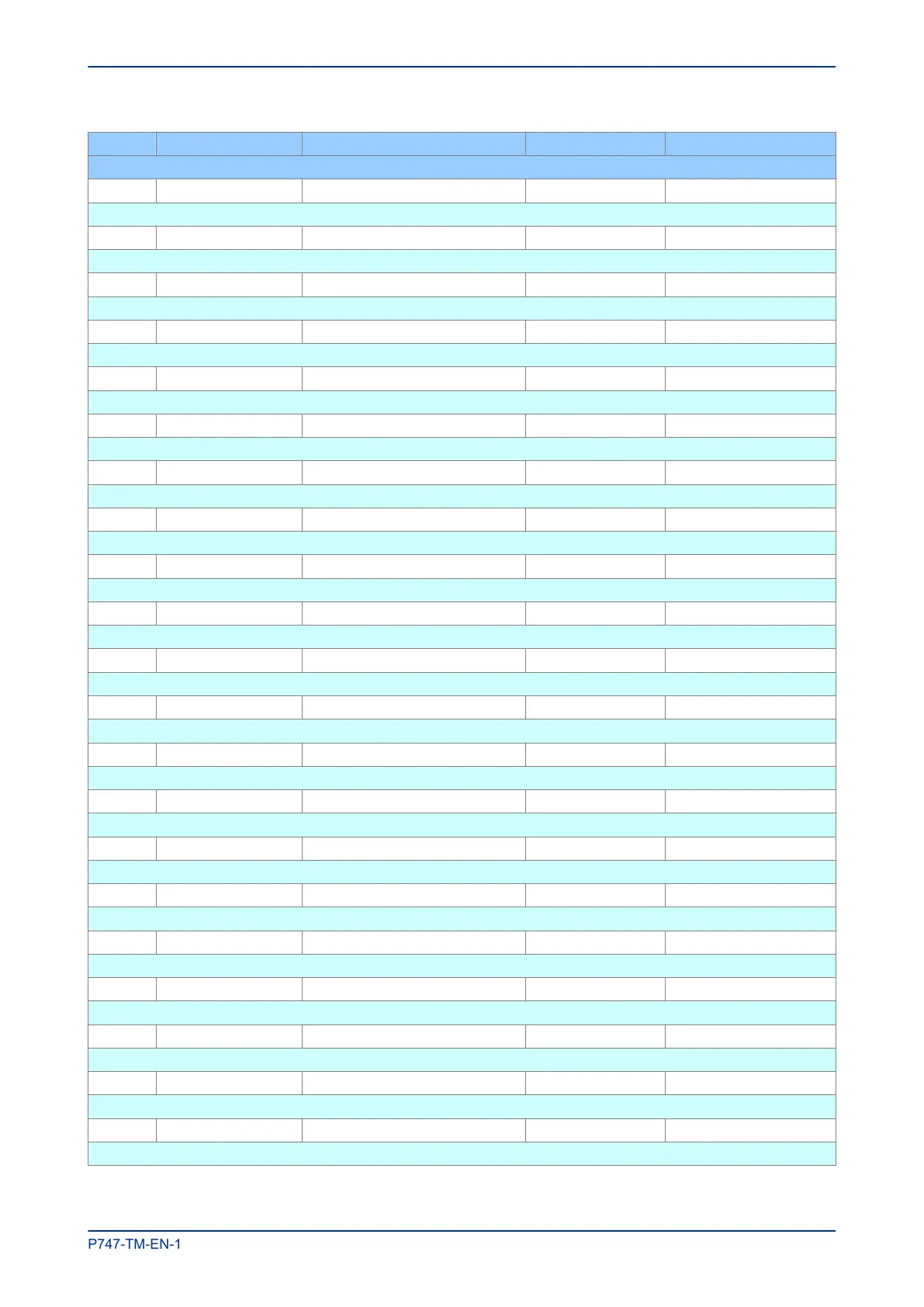

Ordinal Signal Name Source Type Response

Description

298 I>1 Start C Software PSL Input Protection event

This DDB signal is the first stage C-phase Overcurrent start signal

299 I>2 Start Software PSL Input Protection event

This DDB signal is the second stage any-phase Overcurrent start signal

300 I>2 Start A Software PSL Input Protection event

This DDB signal is the second stage A-phase Overcurrent start signal

301 I>2 Start B Software PSL Input Protection event

This DDB signal is the second stage B-phase Overcurrent start signal

302 I>2 Start C Software PSL Input Protection event

This DDB signal is the second stage C-phase Overcurrent start signal

303 I>3 Start Software PSL Input Protection event

This DDB signal is the third stage any-phase Overcurrent start signal

304 I>3 Start A Software PSL Input Protection event

This DDB signal is the third stage A-phase Overcurrent start signal

305 I>3 Start B Software PSL Input Protection event

This DDB signal is the third stage B-phase Overcurrent start signal

306 I>3 Start C Software PSL Input Protection event

This DDB signal is the third stage C-phase Overcurrent start signal

307 I>4 Start Software PSL Input Protection event

This DDB signal is the fourth stage any-phase Overcurrent start signal

308 I>4 Start A Software PSL Input Protection event

This DDB signal is the fourth stage A-phase Overcurrent start signal

309 I>4 Start B Software PSL Input Protection event

This DDB signal is the fourth stage B-phase Overcurrent start signal

310 I>4 Start C Software PSL Input Protection event

This DDB signal is the fourth stage C-phase Overcurrent start signal

351 VTS Slow Block Software PSL Input No response

This DDB signal is a purposely delayed output from the VTS which can block other functions

358 AR Blk Main Prot Software PSL Input Protection event

This DDB signal, generated by the Autoreclose function, blocks the Main Protection elements (POC, EF1, EF2, NPSOC)

567 I>5 Timer Block Programmable Scheme Logic PSL Output No response

This DDB signal blocks the fifth stage overcurrent time delay

568 I>6 Timer Block Programmable Scheme Logic PSL Output No response

This DDB signal blocks the sixth stage overcurrent time delay

570 I>5 Trip Software PSL Input Protection event

This DDB signal is the fifth stage three-phase Phase Overcurrent trip signal

571 I>5 Trip A Software PSL Input Protection event

This DDB signal is the fifth stage A-phase Phase Overcurrent trip signal

572 I>5 Trip B Software PSL Input Protection event

This DDB signal is the fifth stage B-phase Phase Overcurrent trip signal

573 I>5 Trip C Software PSL Input Protection event

This DDB signal is the fifth stage C-phase Phase Overcurrent trip signal

MiCOM P747 Chapter 5 - Protection Functions

P747-TM-EN-1 135

Loading...

Loading...