I/O Controller Hub

122 Design Guide

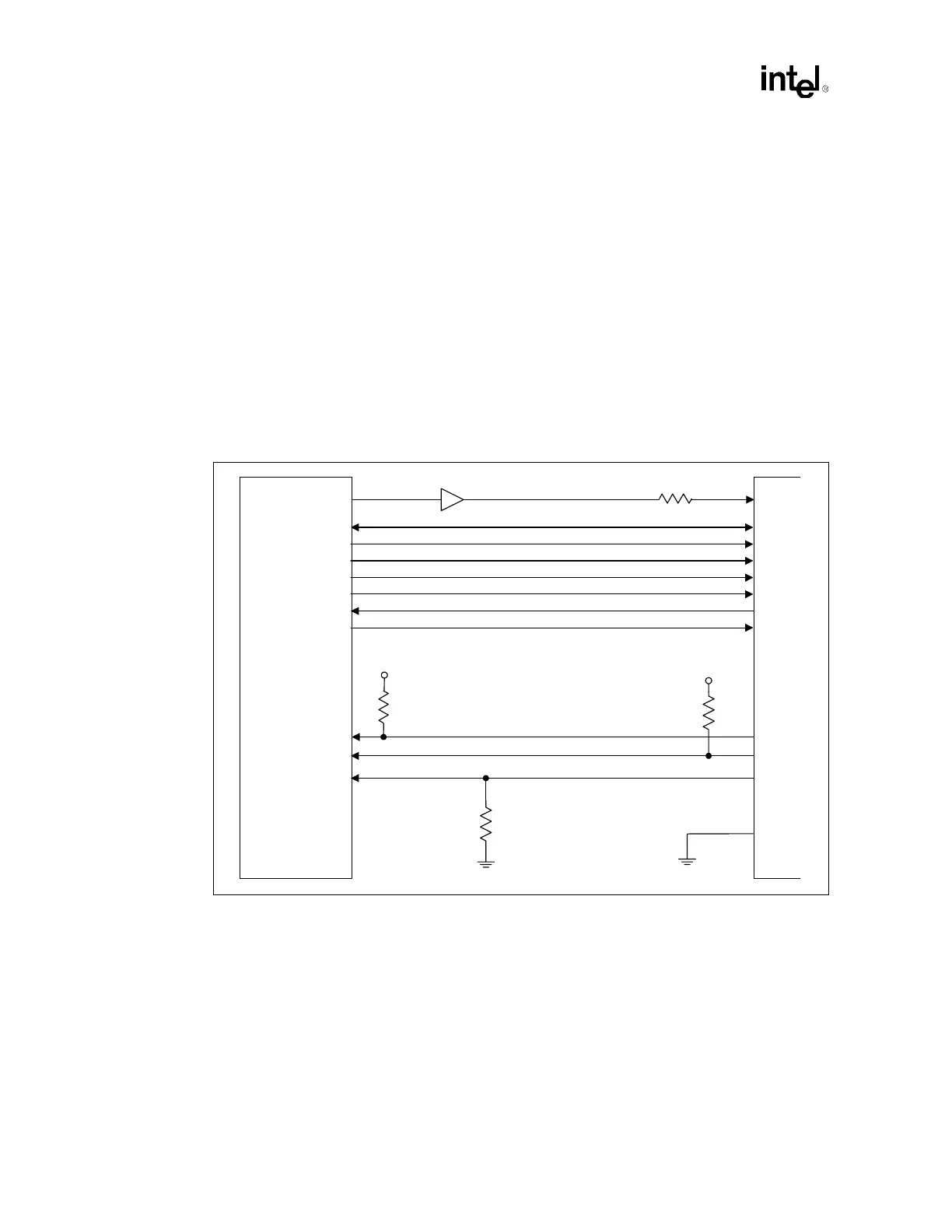

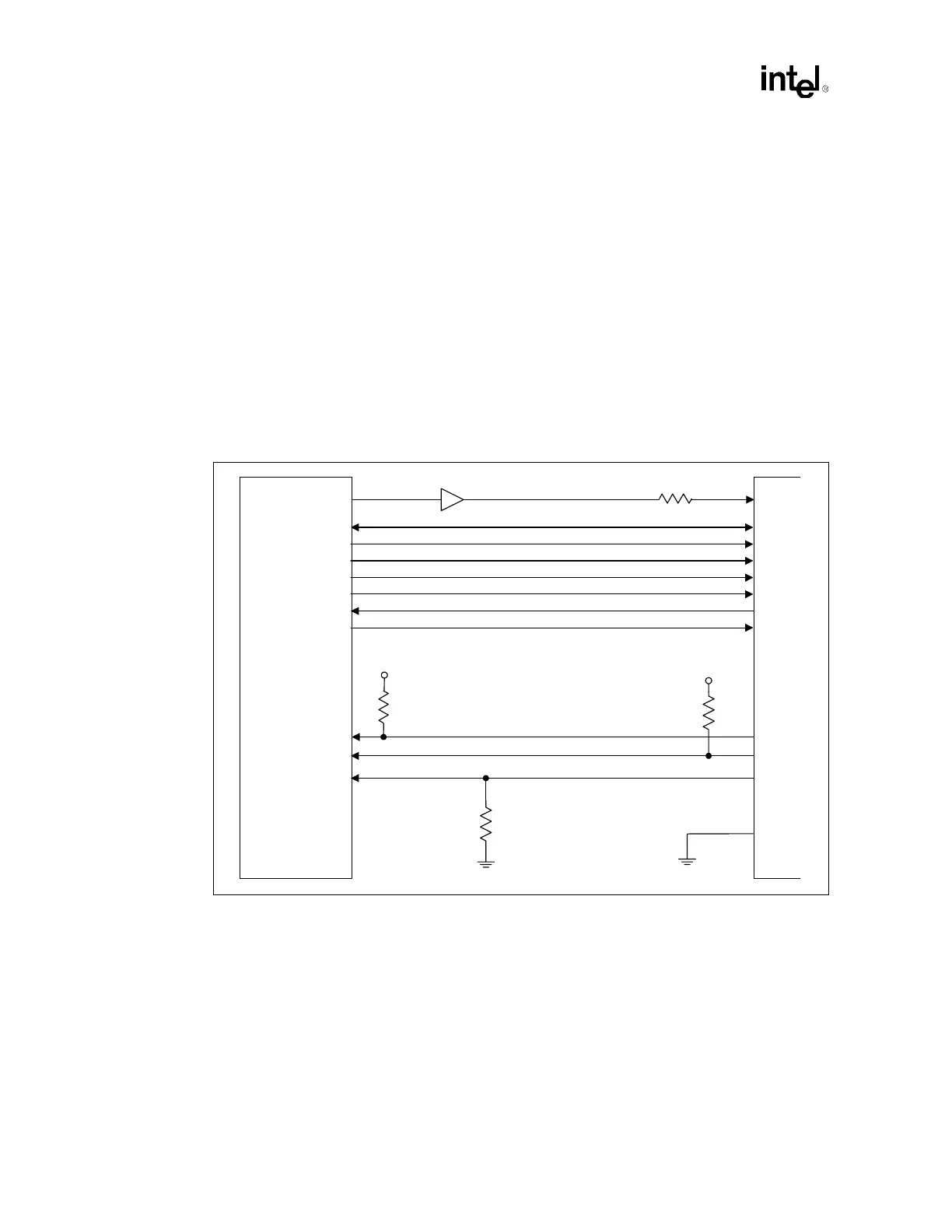

9.1.4 Secondary IDE Connector Requirements

The requirements for the secondary IDE connector are shown in Figure 9-3.

• 22 Ω – 47 Ω series resistors are required on RESET#. The correct value should be determined

for each unique motherboard design, based on signal quality.

• An 8.2 kΩ to 10 kΩ pull-up resistor is required on IRQ15 to VCC_3.3.

• A 4.7 kΩ ± 5% pull-up resistor to VCC_3.3 is required on SIORDY.

• Series resistors can be placed on the control and data lines to improve signal quality. The

resistors are placed as close to the connector as possible. Values are determined for each

unique motherboard design.

• The 10 kΩ resistor to ground on the PDIAG#/CBLID# signal is required on the Secondary

Connector. This change is to prevent the GPIOx pin from floating if a device is not present on

the IDE interface.

NOTE:

1

Because of ringing, PCIRST# must be buffered.

Figure 9-3. Connection Requirements for Secondary IDE Connector

CSEL

3.3 V

3.3 V

4.7 kΩ 8.2–10 kΩ

10 kΩ

SIORDY (SRDSTB/SWDMARDY#)

SDIAG# / CBLID#

IRQ15

GPIOx

Secondary IDE Connector

Intel

®

ICH3-S

PCIRST#

1

SDD[15:0]

SDA[2:0]

SDCS[3,1]#

SDIOR#

SDIOW#

SDDREQ

SDDACK#

22–47 Ω

IDERST#

Loading...

Loading...