Platform Power Delivery Guidelines

186 Design Guide

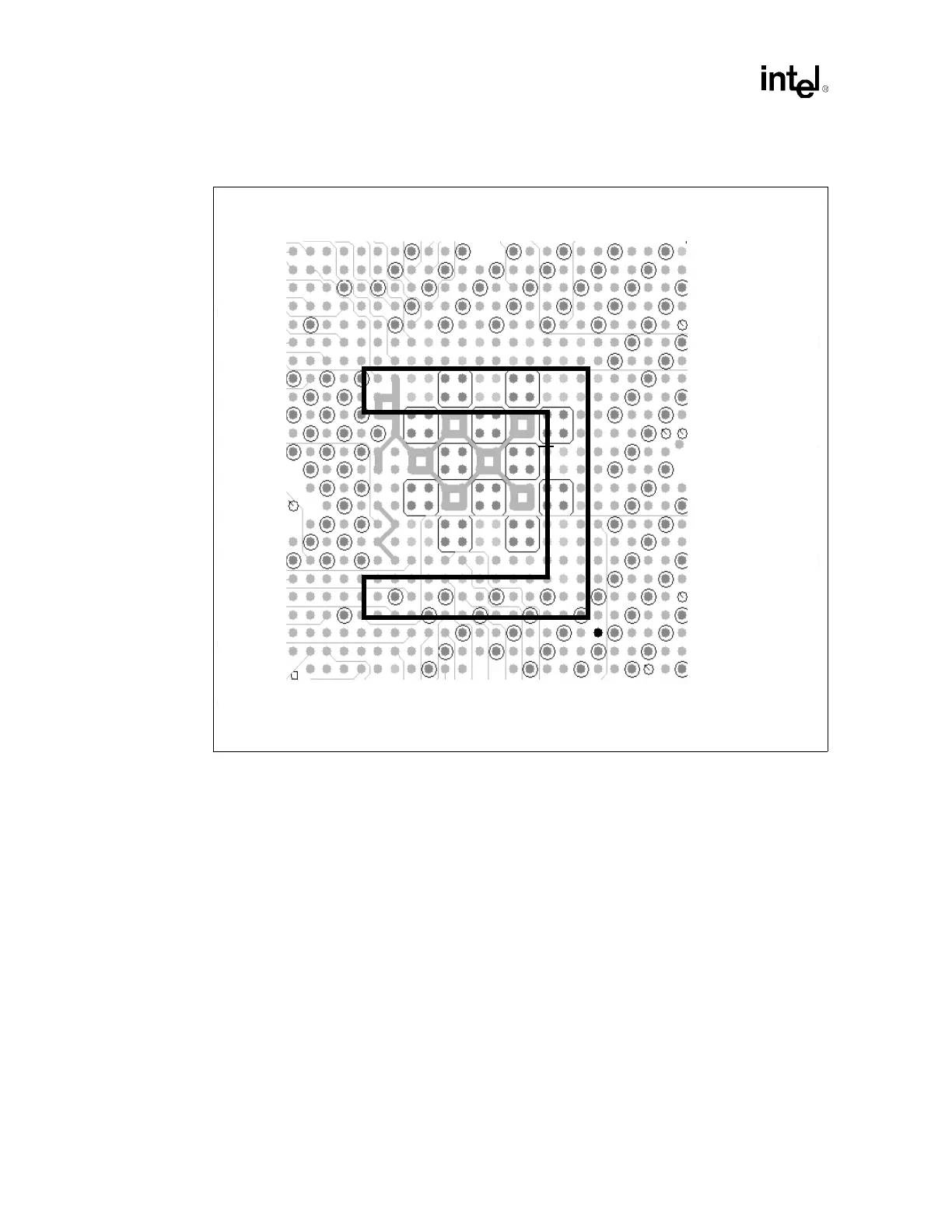

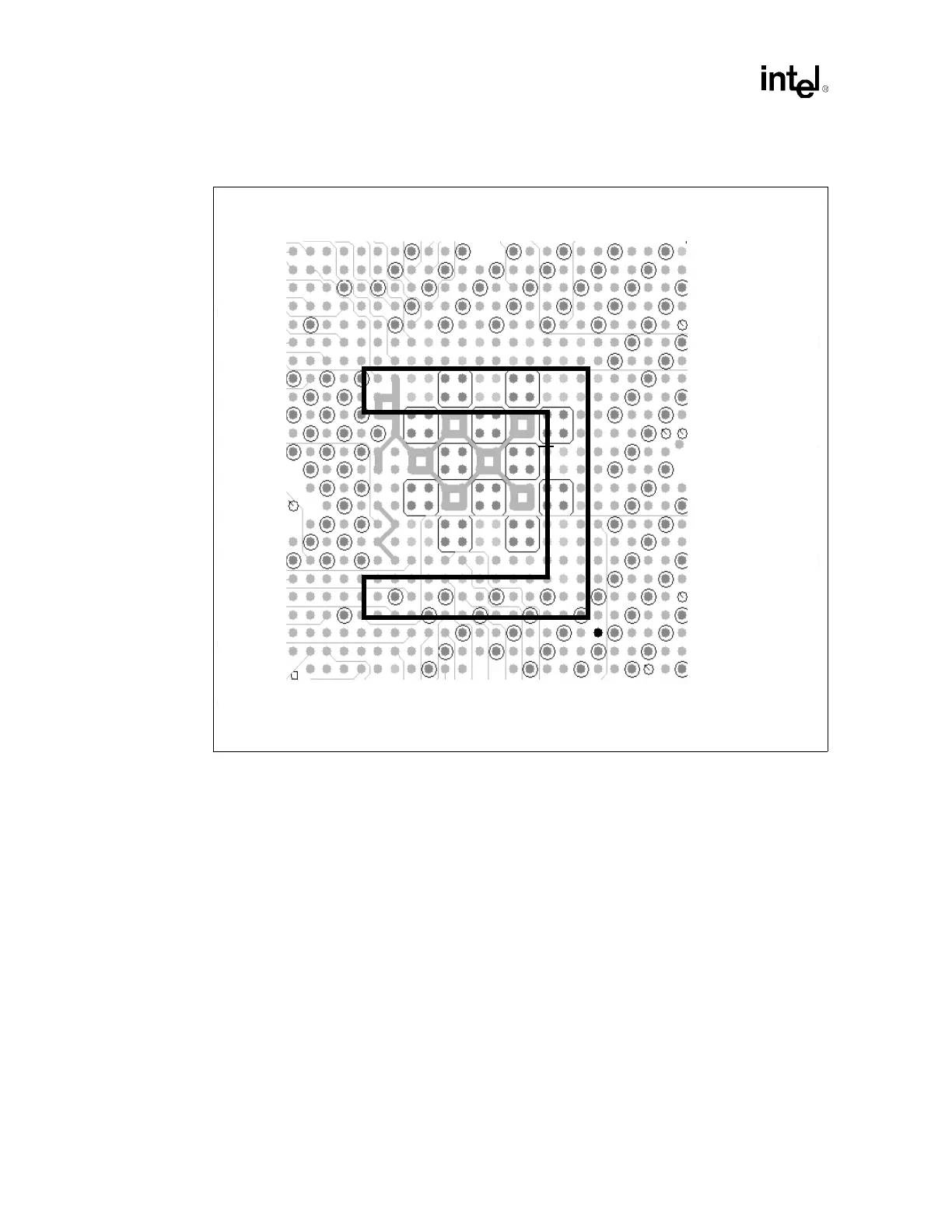

NOTE: The outlined area in the figure is the 3.3 V plane. Place at least five 0.1 µF capacitors in this area.

12.5.3 PCIRST# Implementation

PCI-X requires a 100 ms delay from valid power (PWRGD) to reset deassertion (PCIRST#). The

system design must ensure this requirement is met.

The P64H2 reset must be deasserted within 60 ns of the MCH reset deassertion. Intel strongly

recommends the customer to measure this timing relationship on their board. Failure to meet this

guideline may result in a system failing to boot.

12.5.4 P64H2 Power Sequencing Requirement

3.3 V and 1.8 V must be valid before the first CLK66 pulse is drive to the P64H2. This can be

garunteed by gating the CK408 cocks using a power good signal from the 1.8 V regulator.

Figure 12-23. 3.3V PCI/PCI-X (VCC_3.3) Capacitor Placement

0.1uF

AD24

AD1

A24

A1

Loading...

Loading...