Intel

®

82870P2 (P64H2)

106 Design Guide

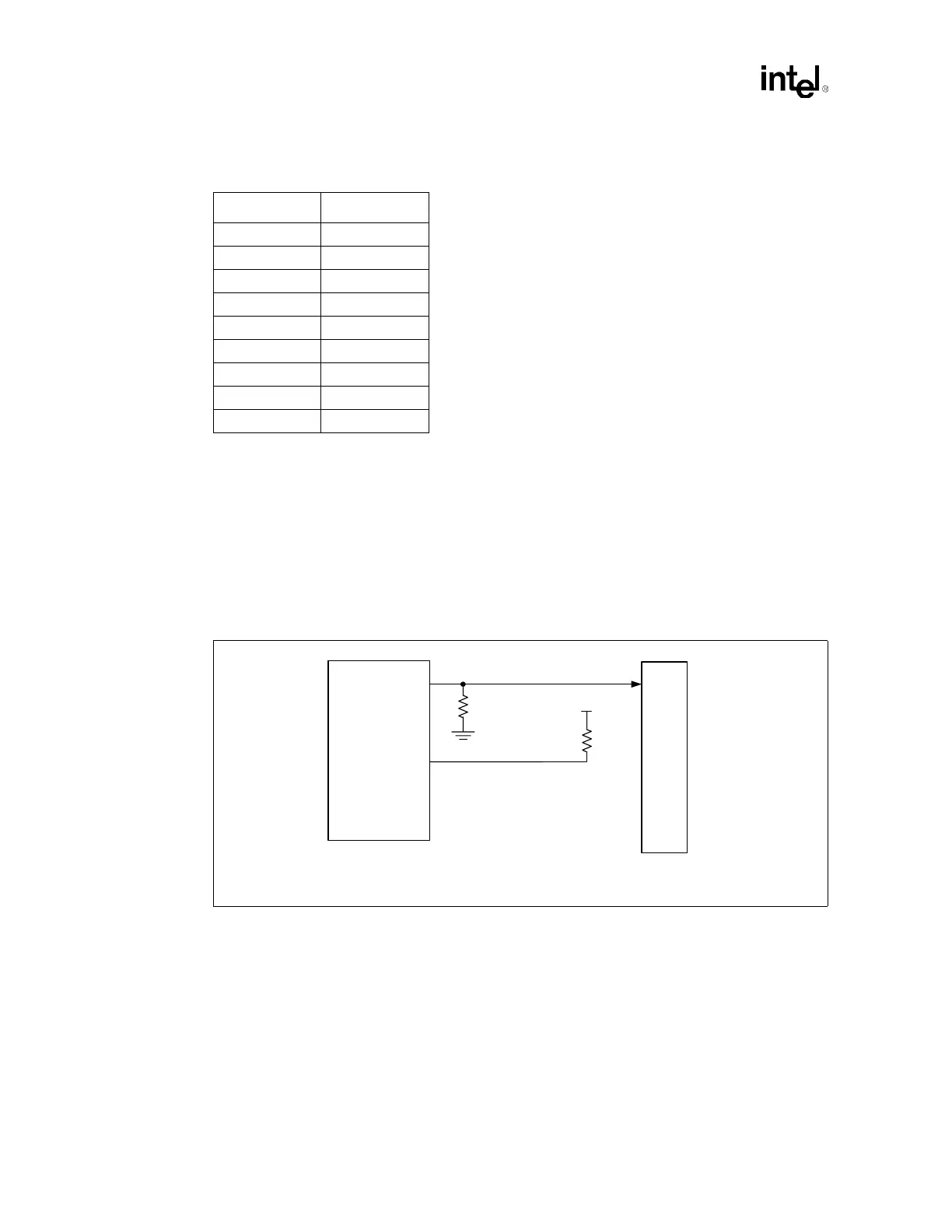

8.2.5.7 SMBus Address Considerations

In Single Slot Parallel mode, the SMBus address strap pins listed in Table 8-7 are muxed with Hot

Plug control signal HxRESETA#. Therefore, it is recommended that the following technique be

used for determining an SMBus address. Pull the PA_GNT5 (RESETA#) signal to ground through

a 100

kΩ ± 5% resistor. This will keep the reset signal active until the P64H2 is ready for it to

become deasserted. Pull the PA_GNT4 (Hx_BUSENB#) signal to 3.3 V through a 10

kΩ ± 5%

resistor. The P64H2 will be able to drive this signal to ground when the signal must be asserted.

8.2.5.8 Pull-Ups/Pull-Downs in Single Slot Parallel Mode

All PCI signals should follow the PCI Local Bus Specification, Revision 2.2 pull-up requirements

whether they are muxed or not. All unused input signals should be pulled to 3.3 V through an

8.2

kΩ ± 5% resistor to keep them from floating.

Table 8-10 defines which muxed signals are to be used with single slot mode. Note that whether in

single or dual slot mode, all signals from Table 8-10 are actually muxed even though only the

signals listed in Table 8-11 are used. As a result, all unused input signals listed in Table 8-10 must

be pulled to 3.3 V through an 8.2

kΩ ± 5% resistor to keep them from toggling.

Table 8-11. Hot Plug Controller Output Signal Reset Values

Signals Reset Value

Px_GNT[5:3] 011

HPx_SOC 0

HPx_SIC 0

HPx_SOL 0

HPx_SOLR 0

HPx_SOD 0

HPx_SORR# 1

HPx_SOR# 0

HPx_SIL# 1

Figure 8-11. Single Slot Parallel SMBus Circuit

HX_BUSENB#

HX_RESETA#

Slot 1

100 kΩ

3.3V

Intel

®

P64H2

10 kΩ

Loading...

Loading...