Platform Clock Routing Guidelines

40 Design Guide

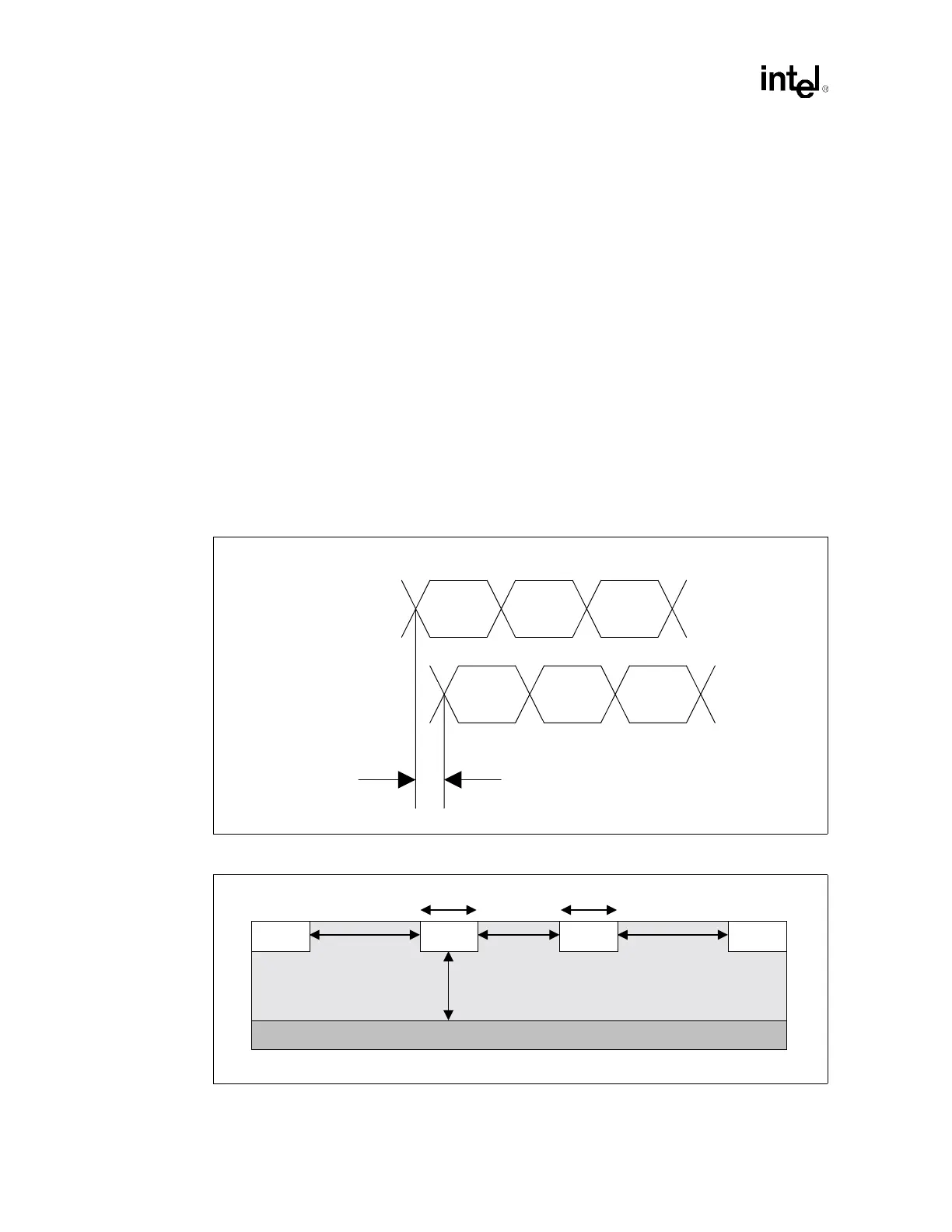

4. Skew measured at the load between any two-bus agents. Measured at the crossing point.

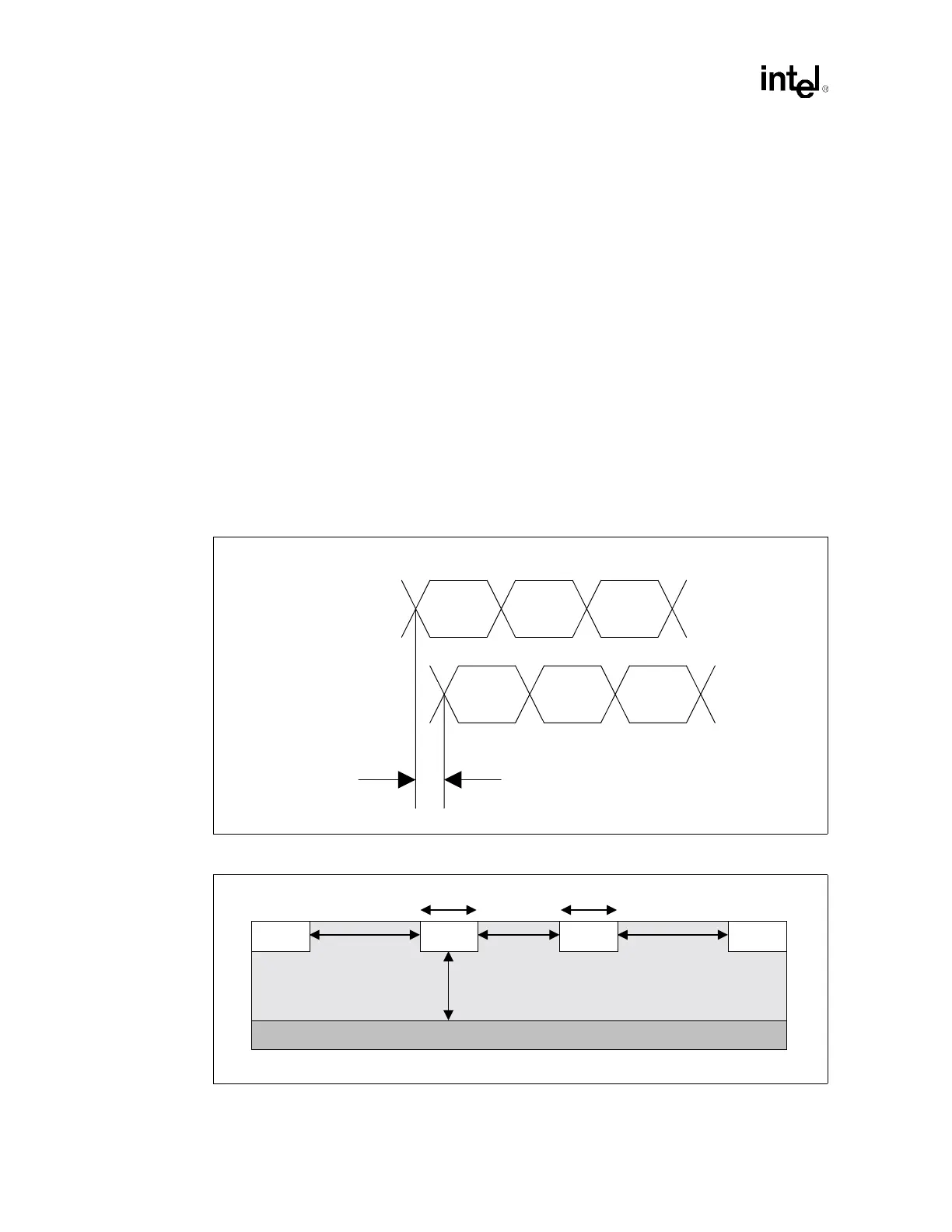

5. Edge to edge spacing between the two traces of any differential pair. Uniform spacing should be maintained

along the entire length of the trace.

6. Clock traces are routed in a differential configuration. Maintain the minimum recommended spacing between

the two traces of the pair. Do not exceed the maximum trace spacing because this degrades the noise

rejection of the network.

7. Set line width to meet correct motherboard impedance. The line width value provided here is a

recommendation to meet the proper trace impedance based on the recommended stack up.

8. The differential impedance of each clock pair is approximately 2*Zsingle-ended*(1-2*Kb) where Kb is the

backwards cross-talk coefficient. For the recommended trace spacing, Kb is very small, and the effective

differential impedance is approximately equal to 2 times the single-ended impedance of each half of the pair.

9. The single ended impedance of both halves of a differential pair should be targeted to be of equal value. They

should have the same physical construction. If the HOST_CLK traces vary within the tolerances specified,

both traces of a differential pair must vary equally.

10.Length compensation for the processor socket and package delay is added to chipset routing to match

electrical lengths between the chipset and the processor from the die pad of each. Therefore, the

motherboard trace length for the chipset will be longer than that for the processor.

11.Rs values between 20

Ω and 33 Ω have been shown to be effective.

12.Rt shunt termination value should match the motherboard impedance.

13.Minimize L1, L2 and L3 lengths. Long lengths on L2 and L3 degrade effectiveness of source termination and

contribute to ringback.

14.The goal of constraining all bus clocks to one physical routing layer is to minimize the impact on skew due to

variations in Er and the impedance variations due to physical tolerances of circuit board material.

15.Length of LT for one processor must match the LT of all other HOST_CLK traces to other processor with

specified tolerance.

Figure 4-3. Clock Skew As Measured from Agent to Agent

Figure 4-4. Trace Spacing for HOST_CLK Clocks

BCLK Slew

BCLK at

Processor

BCLK

at CS

h

W

S1S1

BCLK0 BCLK1

Ground Plane

S

W

Loading...

Loading...