Design Guide 77

Memory Interface Routing Guidelines

6.6 Clock Enable Routing

The MCH provides a single clock enable (CKE) signal. This signal is used during initialization to

indicate that valid power and clocks are being applied to the DIMMs. Because the CKE signal has

higher loading, it requires a lower impedance. The recommended impedance for the CKE signal is

40 Ω. This can be achieved using a 7.5 mil wide trace on the recommended stackup (refer to

Figure 6-3). It is acceptable to route the CKE signal 5 mils wide when breaking out of the MCH.

The CKE signal requires a parallel termination resistor (Rtt) to DDR VTERM placed as close to

the last DIMM connector as possible.

NOTE: Indicated lengths measure from the MCH pin to the DIMM connector pin.

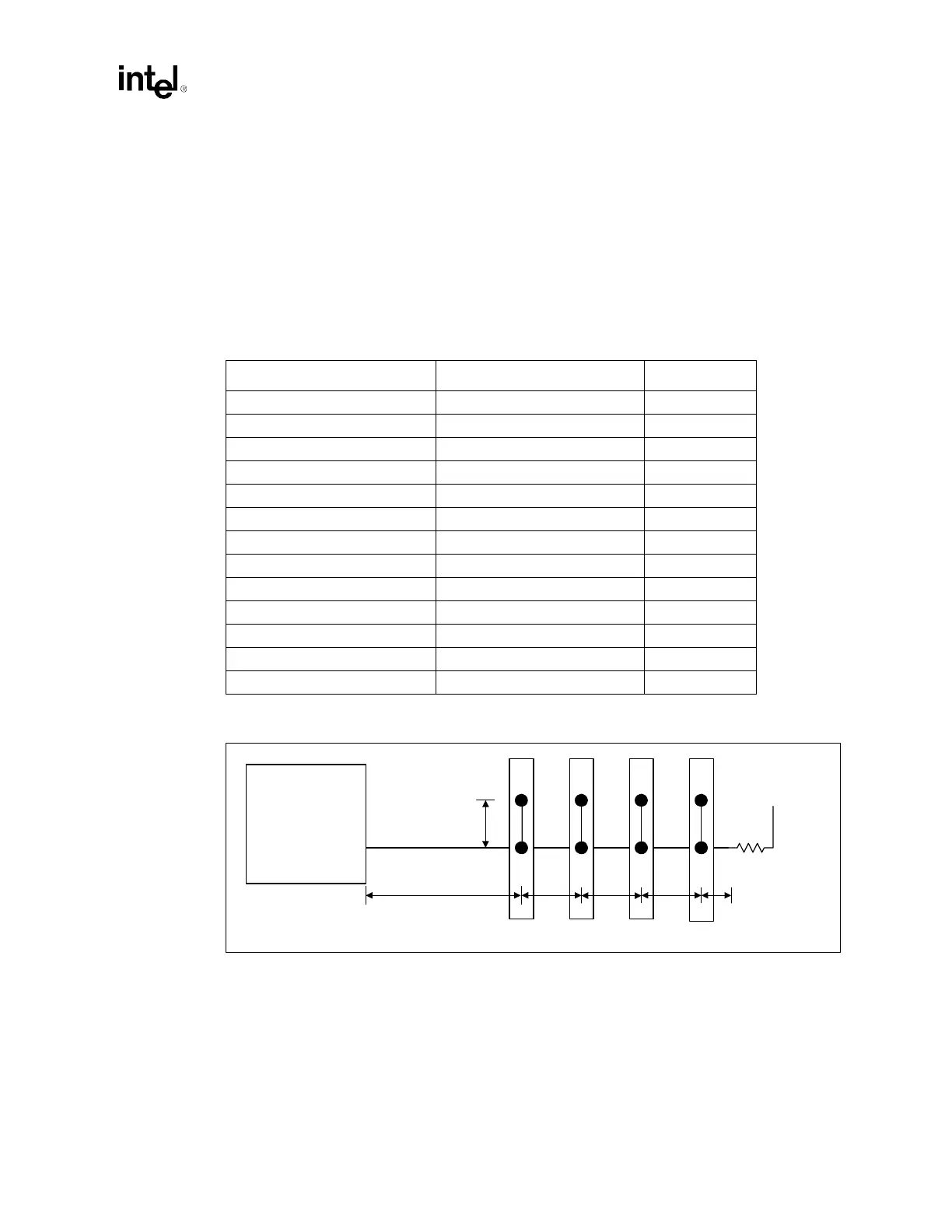

Table 6-7. Clock Enable Routing Guidelines

Parameter Intel

®

E7500 Reference

Signal Group CKE

Topology Daisy Chain with Stubs Figure 6-12

Reference Plane Ground Figure 6-3

Trace Impedance (Zo) 40

Ω ± 10% Figure 6-3

Nominal Trace Width 7.5 mil Figure 6-3

Nominal Trace Spacing 15 mil Figure 6-3

Trace Length – MCH to DIMM1 1.8” to 6.0” Figure 6-12

Trace Length – DIMM to DIMM 0.8” to 1.2” Figure 6-12

Trace Length – CKE Stub < 300 mil Figure 6-12

Trace Length – DIMM to Rtt < 0.8” Figure 6-12

Termination Resistor (Rtt) 22

Ω ± 2% Figure 6-12

MCH Breakout Guidelines 5/5, < 500 mil

Length Tuning Requirements To CMDCLK pair: ± 2.0” Figure 6-9

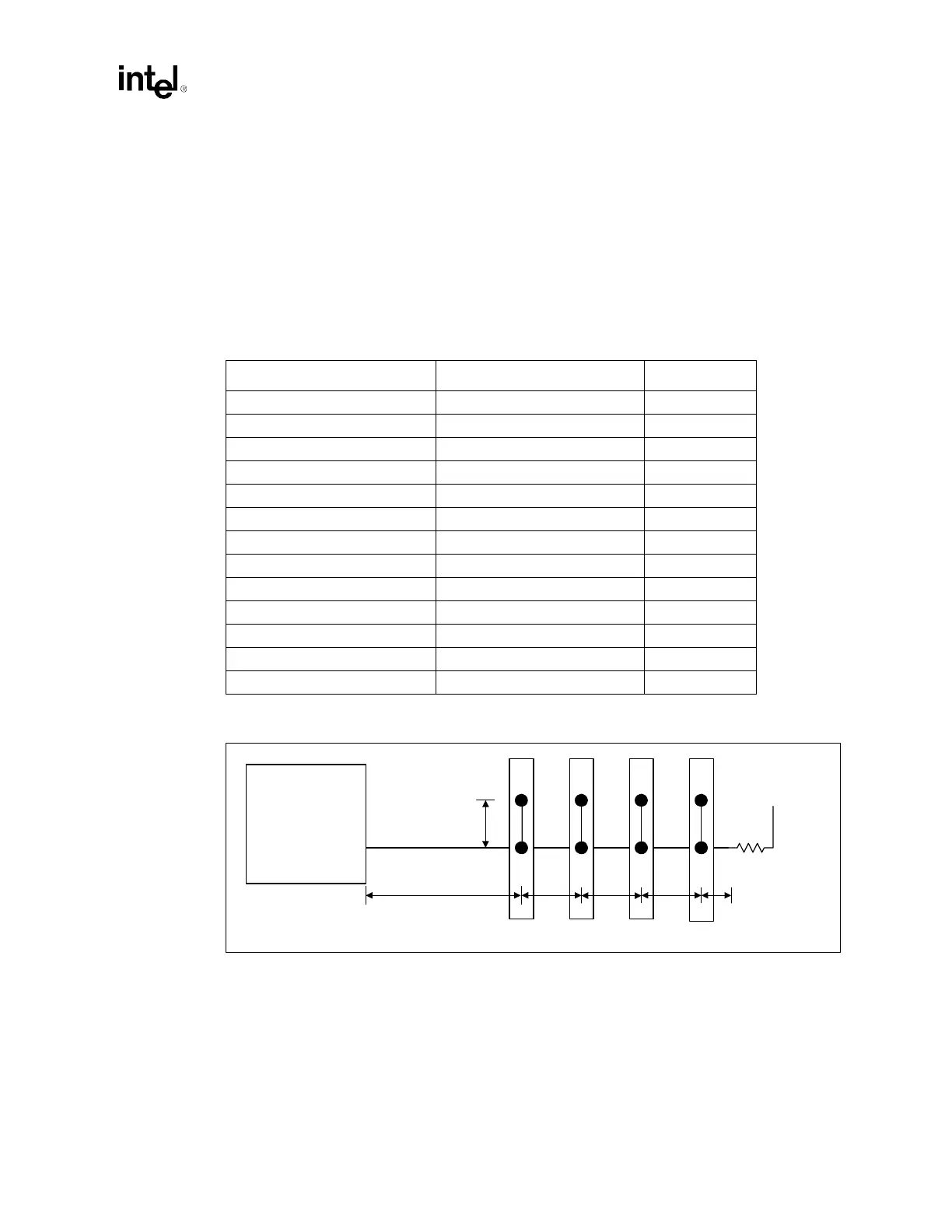

Figure 6-12. CKE Topology

CKE

MCH

DDR VTERM

(1.25V)

DIMMs

DIMM to

DIMM

Rtt

DIMM to

DIMM

DIMM to

DIMM

MCH to DIMM1

DIMM

to Rtt

CKE Stub

Loading...

Loading...