Memory Interface Routing Guidelines

68 Design Guide

6.1 DDR Overview

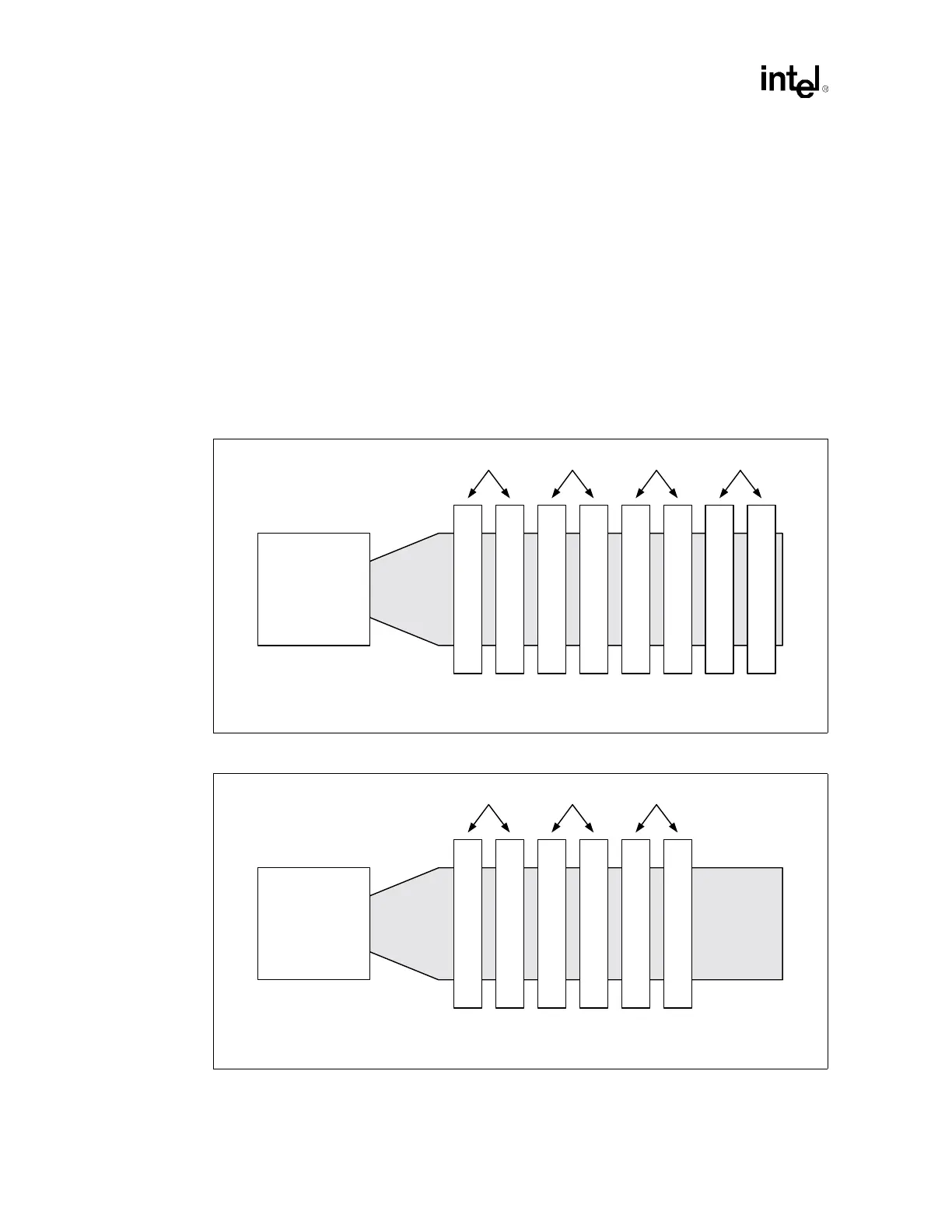

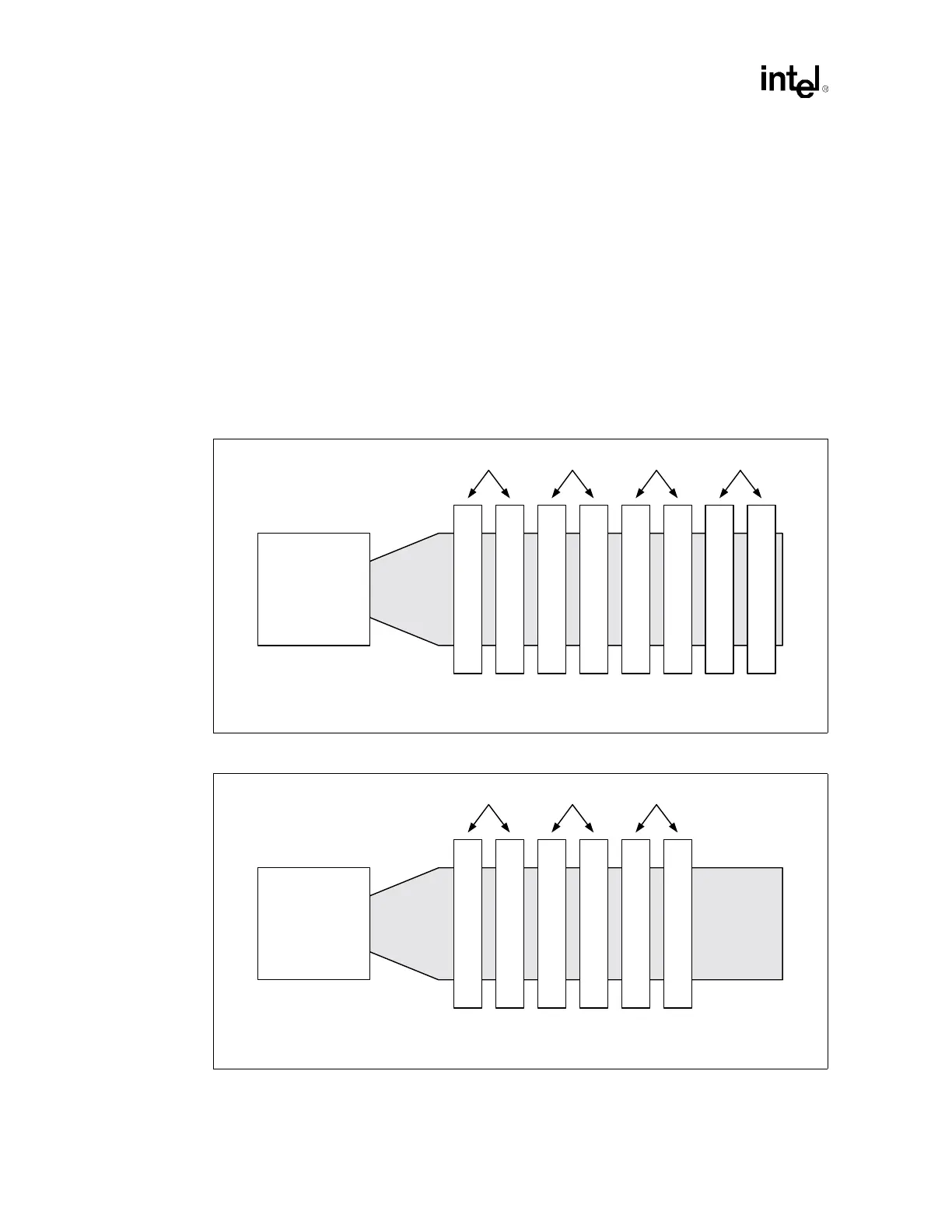

Figure 6-2 and Figure 6-1 show both channels being routed to a single “bank” of eight DIMMs.

The DIMMs are physically interleaved. Intel recommends using this ordering, starting with

Channel B closest to the MCH, for optimal routing.

The platform requires DDR DIMMs to be populated in-order, starting with the 2 DIMMs furthest

from the MCH in a “fill-farthest” approach (see Figure 6-2 and Figure 6-1). This recommendation

is based on the signal integrity requirements of the DDR interface. Intel’s recommendation is to

conduct this check for correct DIMM placement during BIOS initialization. Additionally, it is

strongly recommended that all designs follow the DIMM ordering, SMBus Addressing, Command

Clock routing and Chip Select routing documented in Figure 6-2 and Figure 6-1. This addressing

must be maintained to be compliant with the reference BIOS code supplied by Intel. Designs with

fewer than 3 DIMMs should follow the pattern shown in Figure 6-2 and Figure 6-1.

Figure 6-1. 4 DIMM per Channel Implementation

Figure 6-2. 3 DIMM per Channel Implementation

MCH

D

I

M

M

A4

03h

3/3#

6/7

D

I

M

M

B4

07h

3/3#

6/7

D

I

M

M

A3

02h

2/2#

4/5

D

I

M

M

B3

06h

2/2#

4/5

D

I

M

M

A2

01h

1/1#

2/3

D

I

M

M

B2

05h

1/1#

2/3

D

I

M

M

A1

00h

0/0#

0/1

D

I

M

M

B1

04h

0/0#

0/1

Fill Fourth Fill Third Fill Second Fill First

SMBus Address:

Command Clock:

Chip Select:

MCH

D

I

M

M

A3

02h

2/2#

4/5

D

I

M

M

B3

06h

2/2#

4/5

D

I

M

M

A2

01h

1/1#

2/3

D

I

M

M

B2

05h

1/1#

2/3

D

I

M

M

A1

00h

0/0#

0/1

D

I

M

M

B1

04h

0/0#

0/1

Fill Third Fill Second Fill First

SMBus Address:

Command Clock:

Chip Select:

Loading...

Loading...