Design Guide 47

Platform Clock Routing Guidelines

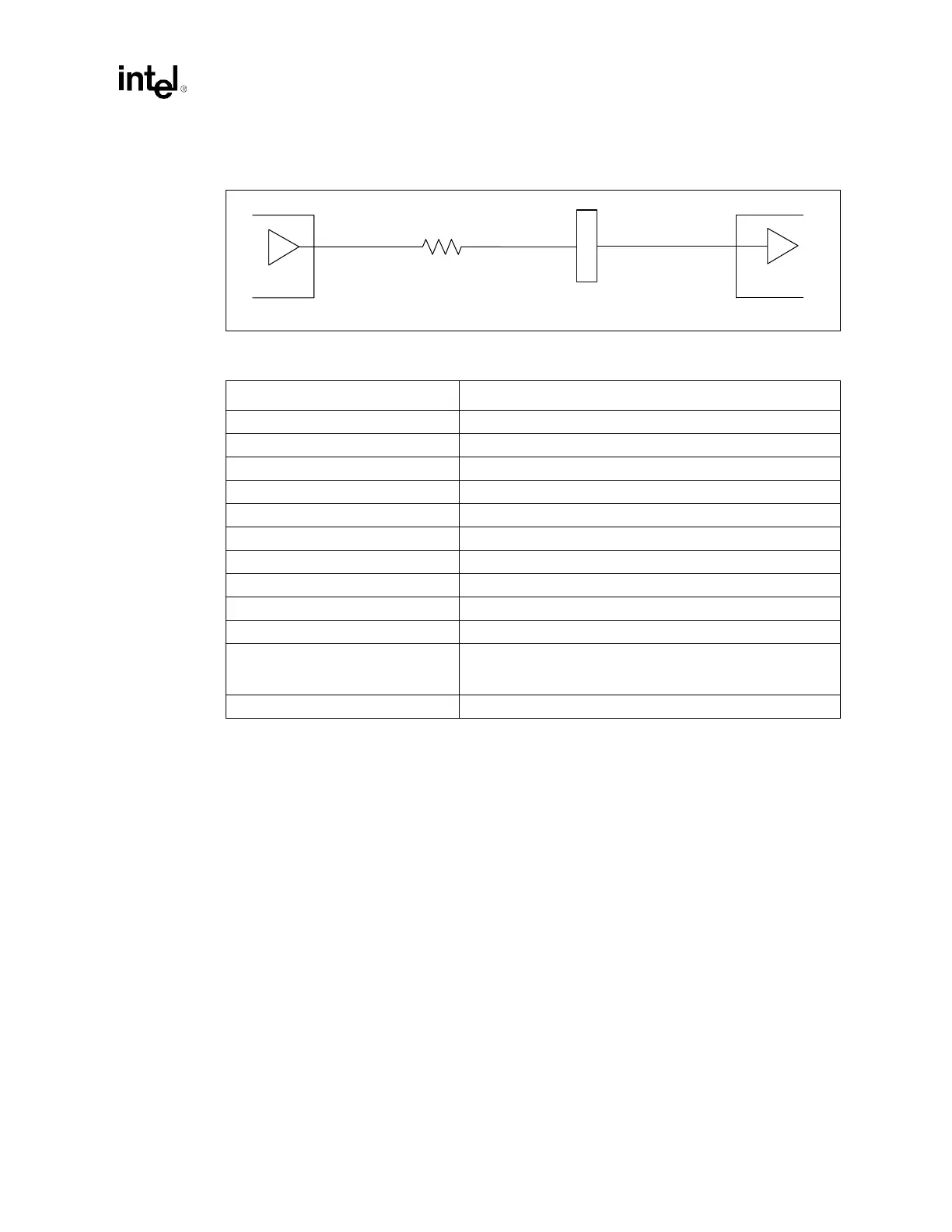

Figure 4-12. Topology for CLK33 to PCI Slot

Table 4-7. CLK33 Routing Guidelines for PCI Slot

Parameter Routing Guidelines

Clock Group CLK33

Topology Point-to-Point

Reference Plane Ground referenced (contiguous over entire length)

Characteristic Trace Impedance (Z

0

) 50 Ω ± 10%

Trace Width 5 mils

Trace Spacing 10 mils

Trace Length – L1 0.00” – 0.50”

Trace Length – L2 3.00” – 9.0”

Trace Length – C Routed 2.50” per

PCI Local Bus Specification, Rev 2.2

Resistor R1 = 33 Ω ± 5%

Skew Requirements PCI device – PCI device skew max allowed by

PCI Local Bus

Specification, Rev 2.2

is 2 ns. Therefore, length match with other

CLK33 signals within ± 1 ns.

Maximum Via Count Per Signal 1

R1

L1 L2

Clock

Driver

PCI Device

C

PCI

Connector

Trace On

PCI Card

Loading...

Loading...