Design Guide 53

System Bus Routing Guidelines

System Bus Routing Guidelines 5

This section covers the system bus source synchronous (data, address, and associated strobes) and

common clock signal routing. Table 5-1 lists the signals and their corresponding signal types.

NOTES:

1. These signals do not have on-die termination on the processor. They must be terminated properly on the

motherboard. If the signal is not connected, it must be pulled to the appropriate voltage level through a

1 k

Ω ± 5% resistor.

2. Xeon processors use only BR0# and BR1#.

3. These signals are ‘wired-OR’ signals and may be driven simultaneously by multiple agents. For further details

on how to implement wired-OR signals, refer to the routing guidelines in Section 5.2.1.

4. The value of these pins during the active edge of RESET# determine processor configuration options.

5. SM_VCC has critical power sequencing requirements.

6. Terminations and routing for TAP signals and all debug port signals are found in the

ITP700 Debug Port

Design Guide

.

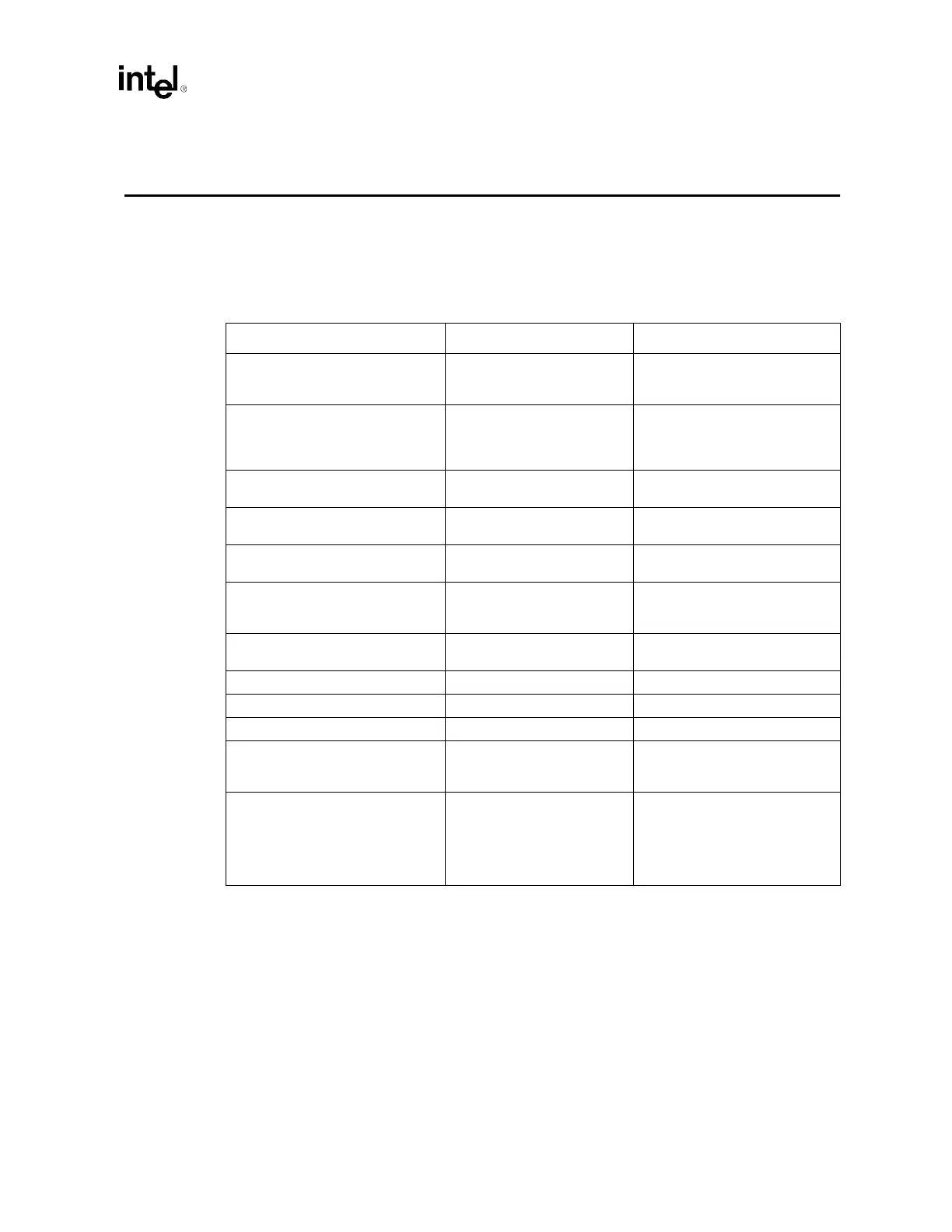

Table 5-1. System Bus Signal Groups

Signal Group Type Signals

AGTL+ Common Clock Input Synchronous to BCLK

BPRI#, BR[3:1]#

1,2

, DEFER#,

RESET#

1

, RS[2:0]#, RSP#,

TRDY#

AGTL+ Common Clock I/O Synchronous to BCLK

ADS#, AP[1:0]#, BINIT#

3

, BNR#

3

,

BPM[5:0]#

1

, BR0#

1

, DBSY#,

DP[3:0]#, DRDY#, HIT#

3

, HITM#

3

,

LOCK#, MCERR#

3

AGTL+ Source Synchronous I/O: 4X

Group

Synchronous to assoc. strobe D[63:0]#, DBI[3:0]#

AGTL+ Source Synchronous I/O: 2X

Group

Synchronous to assoc. strobe A[35:3]#

4

, REQ[4:0]#

AGTL+ Strobes Synchronous to BCLK [1:0]

ADSTB[1:0]#, DSTBN[3:0]#,

DSTBP[3:0]#

Async GTL+ Input

1

Asynchronous

A20M#, IGNNE#, INIT#

4

, LINT0/

INTR, LINT1/ NMI, PWRGOOD,

SMI#

4

, CPUSLP#, STPCLK#

Async GTL+ Output

1

Asynchronous

FERR#, IERR#, PROCHOT#,

THERMTRIP#

System Bus Clock Clock BCLK0, BCLK1

TAP Input

6

Synchronous to TCK TCK, TDI, TMS, TRST#

TAP Output

6

Synchronous to TCK TDO

SMBus Interface

1

Synchronous to SM_CLK

SM_EP_A[2:0], SM_TS_A[1:0],

SM_DAT, SM_CLK, SM_ALERT#,

SM_WP

Power/Other Power/Other

GTLREF[3:0], COMP[1:0], ODTEN,

RESERVED, SKTOCC#,

TESTHI[6:0], VID[4:0], VCC_CPU,

SM_VCC

5

, VCCA, VSSA,

VCCIOPLL, VSS, VCCSENSE,

VSSSENSE

Loading...

Loading...