Design Guide 135

I/O Controller Hub

9.7.1 LCI (LAN Connect Interface) Guidelines

This section contains guidelines on how to implement a PLC (Platform LAN Connect) device on a

system motherboard using LCI. It should not be treated as a specification, and the system designer

must ensure through simulations or other techniques that the system meets the specified timings.

Special care must be given to matching the LAN_CLK traces to those of the other signals, as

shown below. The following are guidelines for the ICH3-S to LAN component interface. The

following signal lines are used on this interface:

• LAN_CLK

• LAN_RSTSYNC

• LAN_RXD[2:0]

• LAN_TXD[2:0]

This interface supports 82562ET/82562EM components. Signal lines LAN_CLK,

LAN_RSTSYNC, LAN_RXD[0], and LAN_TXD[0] are shared by all components.

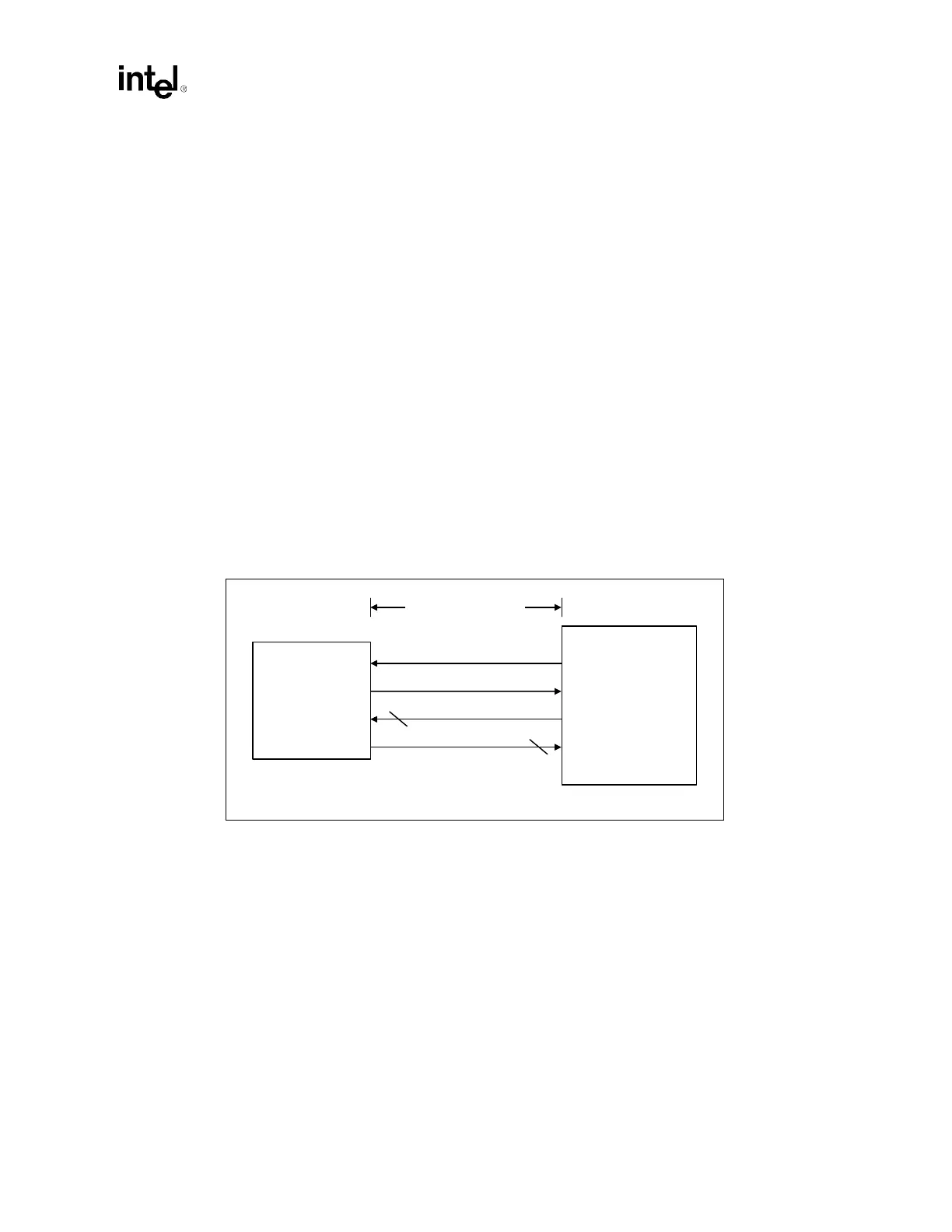

9.7.1.1 Bus Topology

The LAN Connect Interface must be configured in direct point-to-point connection between the

ICH3-S and the LAN component topology. (Refer to Figure 9-15.)

Figure 9-15. Point-to-Point Interconnect Guideline

Intel

®

ICH3-S

Intel

®

82562ET

or

Intel

®

82562EM

L = 4.5" – 10"

LAN_CLK

LAN_RSTSYNC

LAN_RXD[2:0]

LAN_TXD[2:0]

Loading...

Loading...