Schematic Checklist

196 Design Guide

13.3 Intel

®

ICH3-S Schematic Checklist

Note: There are no inputs to the ICH3-S that can be left floating.

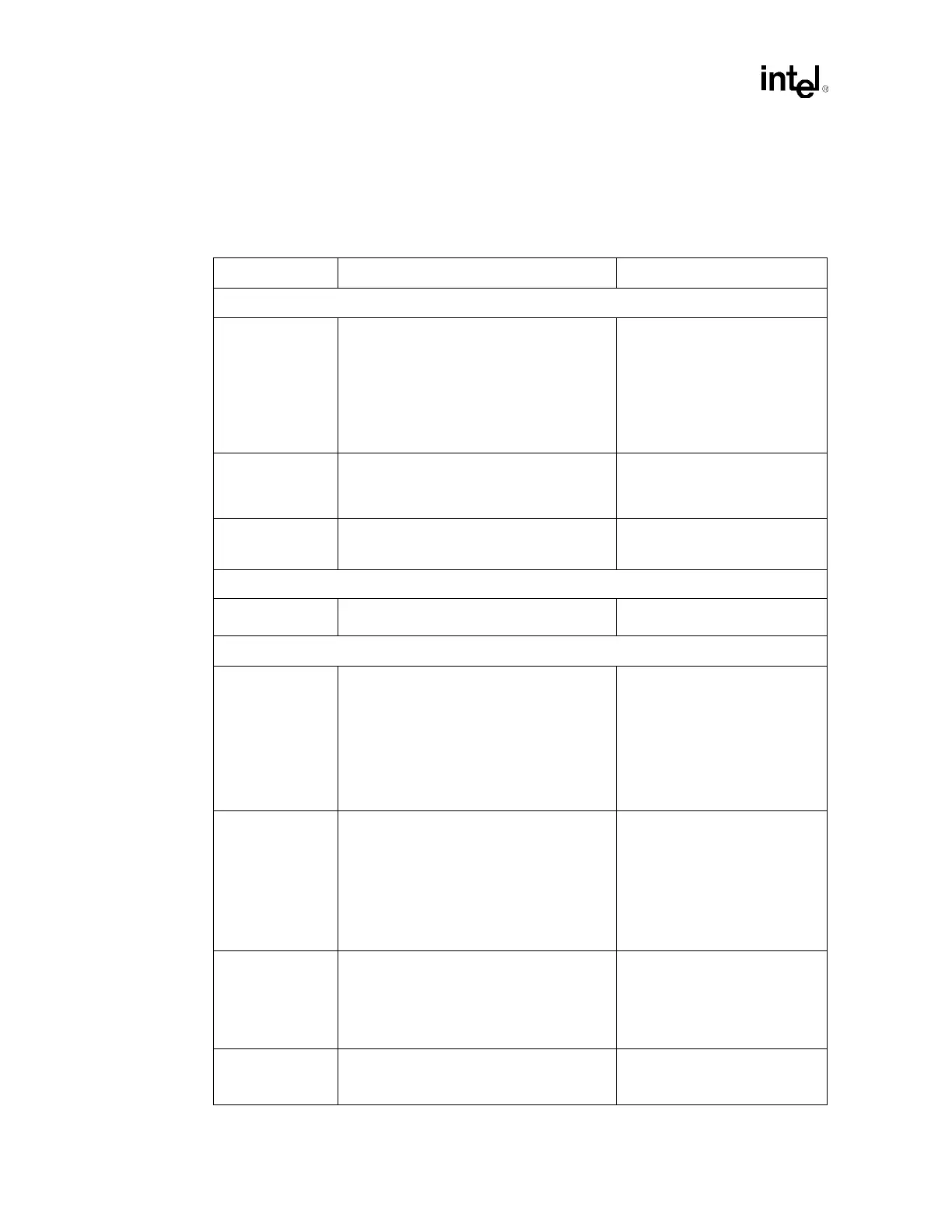

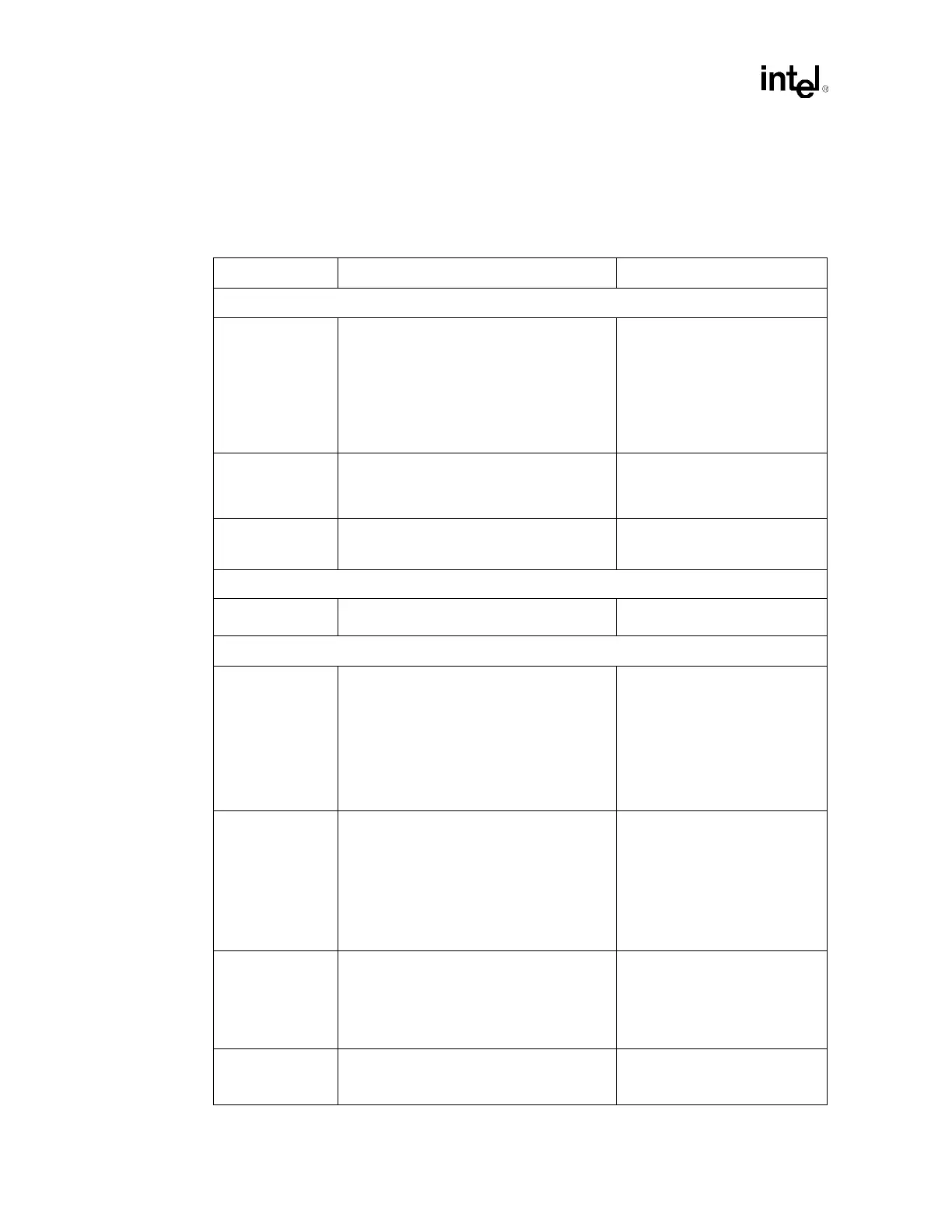

Table 13-3. Intel

®

ICH3-S Schematic Checklist (Sheet 1 of 8)

Checklist Items Recommendations Comments

Processor Signals

A20M#

CPUSLP#

(SLP#)

FERR#

IGNNE#

INIT#

LINT1

1

LINT0

1

SMI#

STPCLK#

• Refer to the signal recommendations under

the Processor Schematic Checklist.

RCIN#

A20GATE

• Pull-up is required if driven by an open drain

signal

(the value of the resistor is determined by

the driver).

• Typically driven by Open Drain

External Micro-controller.

CPUPWRGD • Recommend 300

Ω ± 5% pull-up to

VCC_CPU. Connect to both processors and

ICH3-S.

• Asserted by ICH3-S when all

processor voltage supplies are

stable.

FWH Interface

FWH[3:0]/ LAD[3:0]

LDRQ[1:0]

• No extra pull-ups required. Connect straight

to FWH/LPC and, if supported, a BMC.

• ICH3-S Integrates 24 kΩ pull-up

resistors on these signal lines.

GPIO

GPIO[7:0] • These pins are in the Main Power Well. Pull-

ups must use the VCC_3.3 plane.

• Unused core well inputs must be pulled up

to VCC_3.3.

• GPIO[1:0] can be used as REQ[B:A]#.

• GPIO[1] can be used as PCI REQ[5]#.

• GPIO[5:2] can be used as PIRQ[H:E]#.

• These signals are 5 V tolerant.

• Ensure all unconnected signals

are

outputs only.

GPIO[8] & [13:11] • These pins are in the Resume Power Well.

Pull-ups go to VCC_SUS3.3 plane.

• Unused resume well inputs must be pulled

up to VCC_SUS3.3.

• These are the only GPIs that can be used

as ACPI compliant wake events.

• These signals are not 5 V tolerant.

• GPIO[11] can be used as SMBALERT#.

• These are the only GPI signals

in the resume well with

associated status bits in the

GPE1_STS register.

GPIO[23:16] • Fixed as output only. Can be left NC.

• In Main Power Well.

• GPIO[22] is open drain.

• GPIO[17:16] can be used as GNT[B:A]#.

• GPIO[17] can be used as PCI GNT[5]#.

GPIO[28,27,25,24] • I/O pins. Defaults as an output. Can be left

NC.

• From resume power well. (VCC_SUS3.3).

Loading...

Loading...