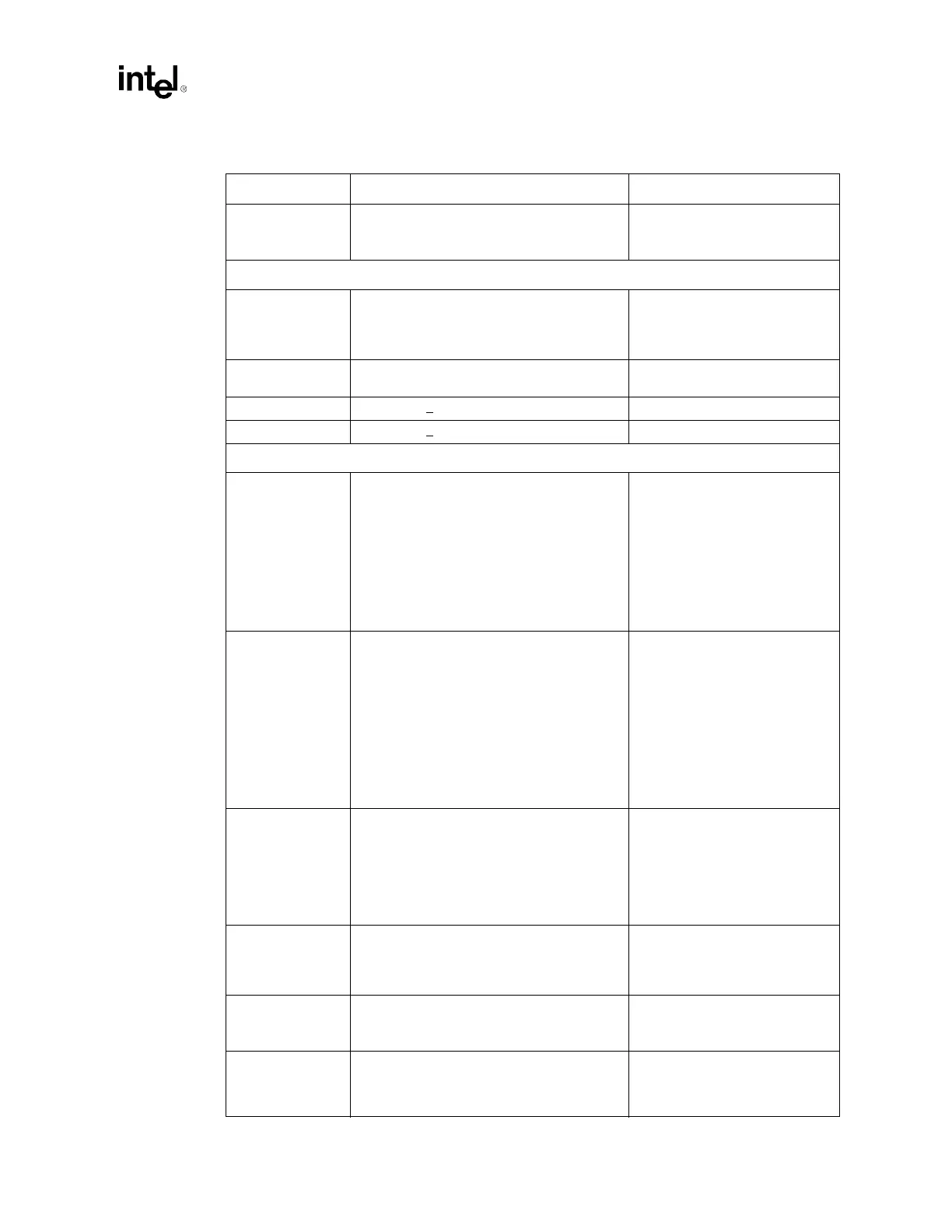

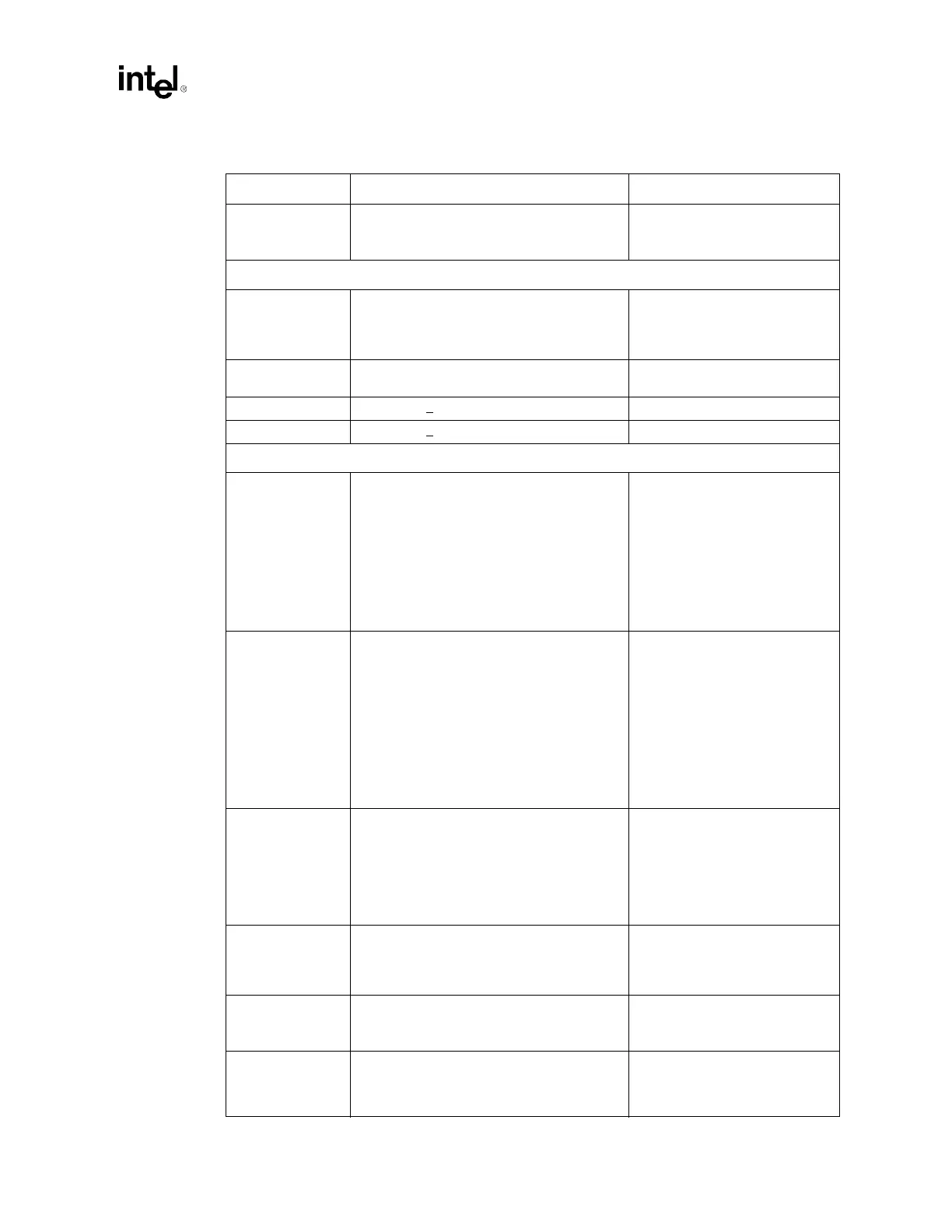

Design Guide 197

Schematic Checklist

GPIO[43:32] • I/O pins. Defaults as an output when

enabled as GPIOs.

• From main power well (VCC_3.3).

Hub Interface

HI[11] • No pull-up resistor required. • Use a no-stuff or a test point to

put the ICH3-S into NAND

chain mode testing.

• Refer to Section 7.3.1.

HICOMP • Tie the pin to a 78.7

Ω ± 1% pull-up resistor

to

VCC_1.8.

• Refer to Section 7.3.3.

HIREF • 0.350 V +

5% • Refer to Section 7.3.2.

HITERM • 0.700 V +

5% • Refer to Section 7.3.2.

IDE Checklist

PDD[15:0]

SDD[15:0]

• No extra series termination resistors or

other pull-ups/pull-downs are required.

• PDD7/SDD7 does not require a 10 k

Ω pull-

down resistor.

• Refer to ATA ATAPI-6

specification.These signals

have integrated series resistors.

• Refer to Section 9.1.3 and

Section 9.1.4.

NOTE: Simulation data indicates

that the integrated series

termination resistors are a nominal

33

Ω, but can range from 31 Ω to

43

Ω.

PDIOW#

PDIOR#

PDDACK#

PDA[2:0]

PDCS1#

PDCS3#

SDIOW#

SDIOR#

SDDACK#

SDA[2:0]

SDCS1#

SDCS3#

• No extra series termination resistors. Pads

for series resistors can be implemented

should the system designer have signal

integrity concerns.

• These signals have integrated

series resistors.

• Refer to Section 9.1.3 and

Section 9.1.4.

NOTE: Simulation data indicates

that the integrated series

termination resistors are a nominal

33

Ω, but can range from 31 Ω to

43

Ω.

PDREQ

SDREQ

• No extra series termination resistors.

• No pull-down resistors required.

• These signals have integrated

series resistors in the ICH3-S.

• These signals have integrated

pull-down resistors in the

ICH3-S.

• Refer to Section 9.1.3 and

Section 9.1.4.

PIORDY

SIORDY

• No extra series termination resistors.

• Pull-up to VCC3.3 via a 4.7

± 5% kΩ

resistor.

• These signals have integrated

series resistors in the ICH3-S.

• Refer to Section 9.1.3 and

Section 9.1.4.

IRQ14

IRQ15

• Recommend 8.2 k

Ω – 10 kΩ pull-up

resistors to VCC3.3.

• No extra series termination resistors.

• Open drain outputs from drive.

• Refer to Section 9.1.3 and

Section 9.1.4.

IDERST# • The PCIRST# signal should be buffered to

form the IDERST# signal. A 33

Ω series

termination resistor is recommended on this

signal.

• Refer to Section 9.1.3 and

Section 9.1.4.

Table 13-3. Intel

®

ICH3-S Schematic Checklist (Sheet 2 of 8)

Checklist Items Recommendations Comments

Loading...

Loading...