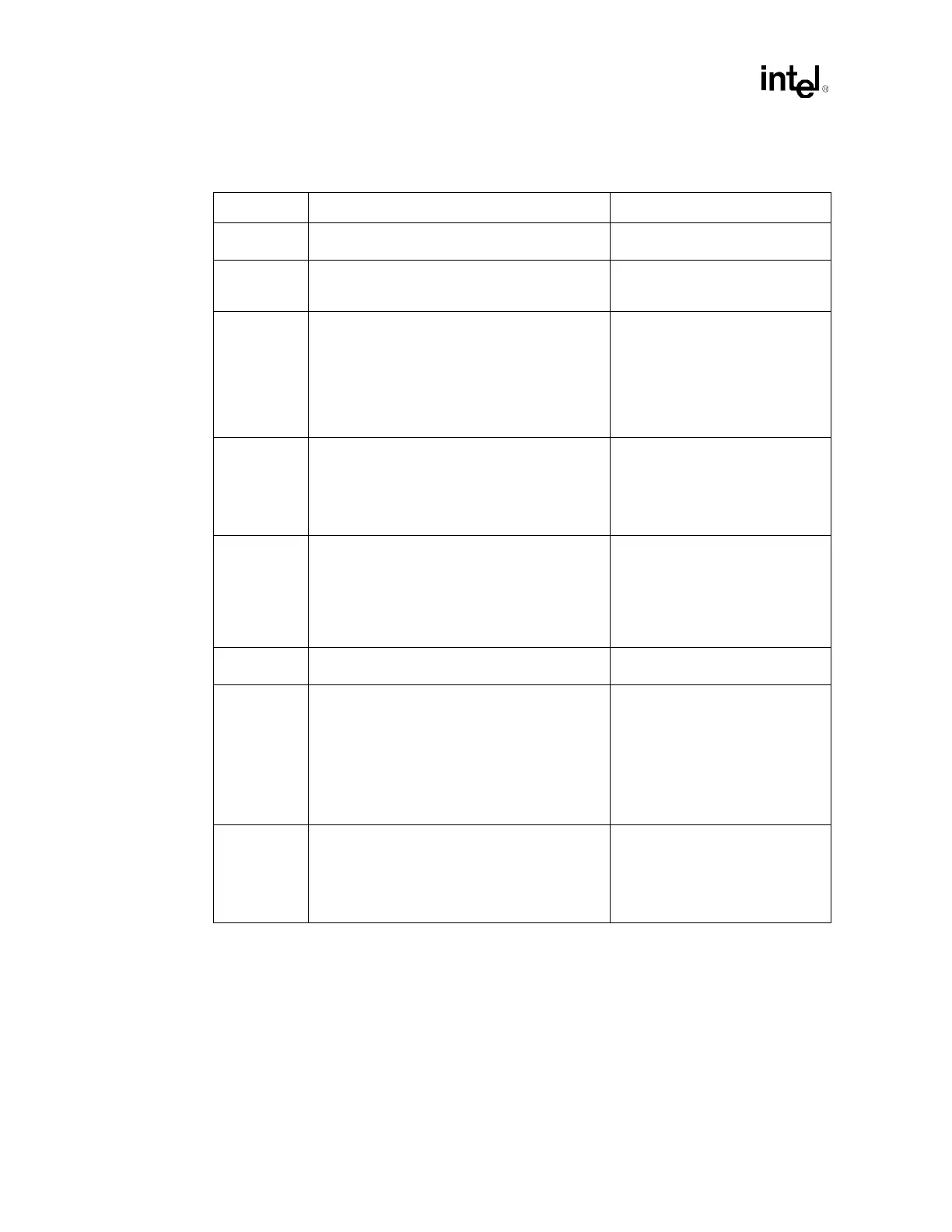

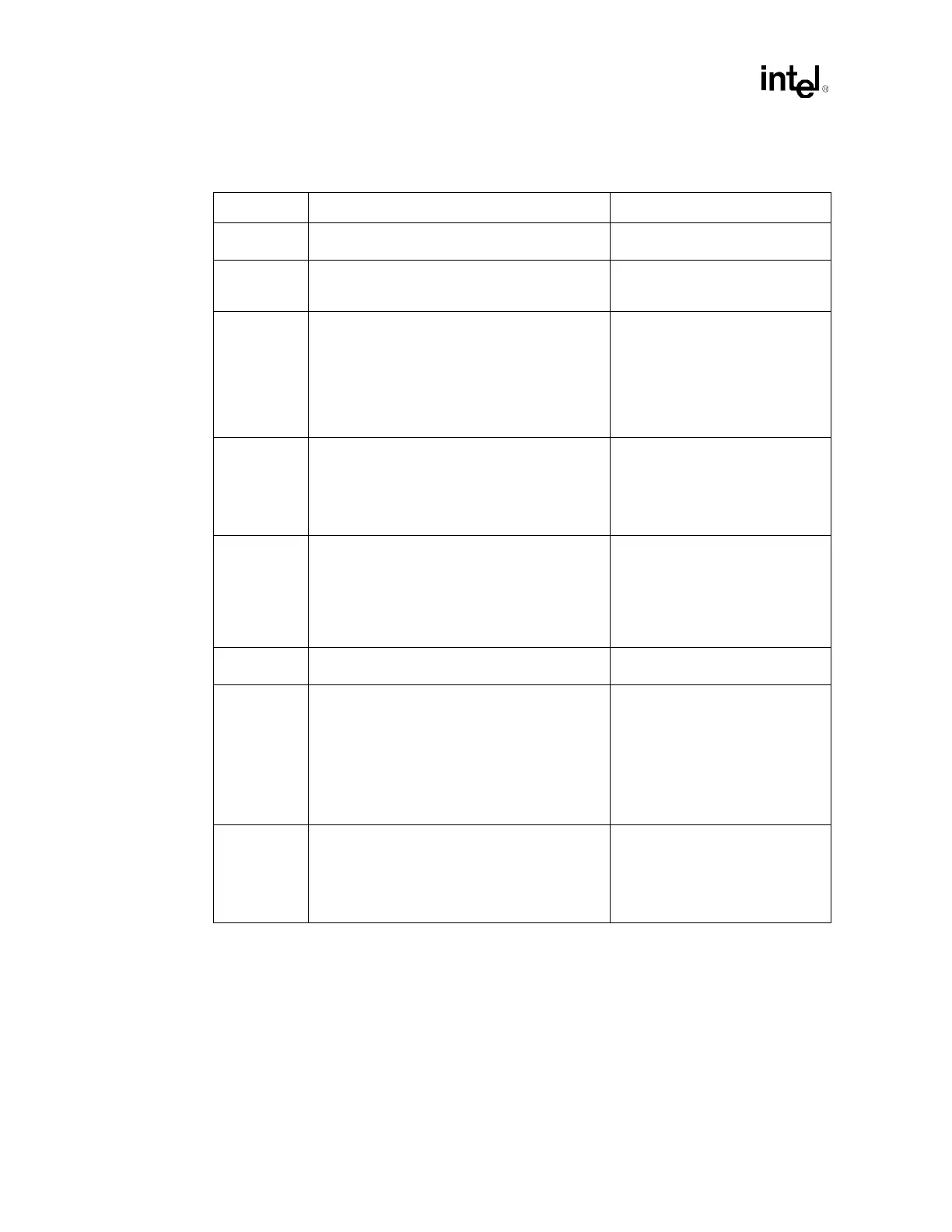

Platform Power Delivery Guidelines

184 Design Guide

Table 12-9. Intel

®

ICH3-S Decoupling Recommendations

Power Decoupling Requirements Decoupling Placement

V_CPU_IO Use one 0.1 µF decoupling capacitor.

• Locate within 100 mils of the

ICH3-S processor interface balls.

VCCRTC

Use

one 1.0 µF decoupling capacitor.

See Figure 9-10 for the External Circuitry.

• Locate within 100 mils of the

VCCRTC interface ball (ball

AB6).

VCC_3.3 Requires

six 0.1 µF decoupling capacitors.

• Distribute around the ICH3-S

package sides within 100 mils of

the package balls:

– Top near AUX/PCI

– Left across the PCI and LPC

– Bottom near IDE

– Right near GPIO[43]

VCCSUS_3.3 Requires

two 0.1 µF decoupling capacitors.

• Place one capacitor on the top

side within 200 mils of the USB

center.

• Place one capacitor on the

bottom side near the

VCCSUS_3.3 supply.

VCC_1.8 Requires

four 0.1 µF decoupling capacitors.

• Locate 2 capacitors distributed

local to the hub interface, within

50 mils of the package HI balls.

• Distribute the remaining

capacitors on the left and bottom

sides of the package for core

delivery.

VCCSUS_1.8 Requires

one 0.1 µF decoupling capacitor.

• Locate within 200 mils of the

ICH3-S, Balls B23 and C23.

5VREF_SUS

Requires

one 0.1 µF decoupling capacitor.

V5REF_SUS is the reference voltage for some 5 V

tolerant inputs in the ICH3-S (USB data and over

current signals). V5REF_SUS must power up before

or simultaneous to VCCSUS_3.3. It must power

down after or simultaneous to VCCSUS_3.3. (For

most platforms, this power sequencing is not an

issue as VCCSUS_3.3 is derived from

5VREF_SUS.)

V5_REF

Requires

one 0.1 µF decoupling capacitor.

V5_REF is the reference voltage for most 5 V

tolerant inputs in the ICH3-S. Tie to pins V5REF[2:1].

V5REF must power up before or simultaneous to

VCC_3.3. It must power down after or simultaneous

to VCC_3.3.

Loading...

Loading...