Design Guide 75

Memory Interface Routing Guidelines

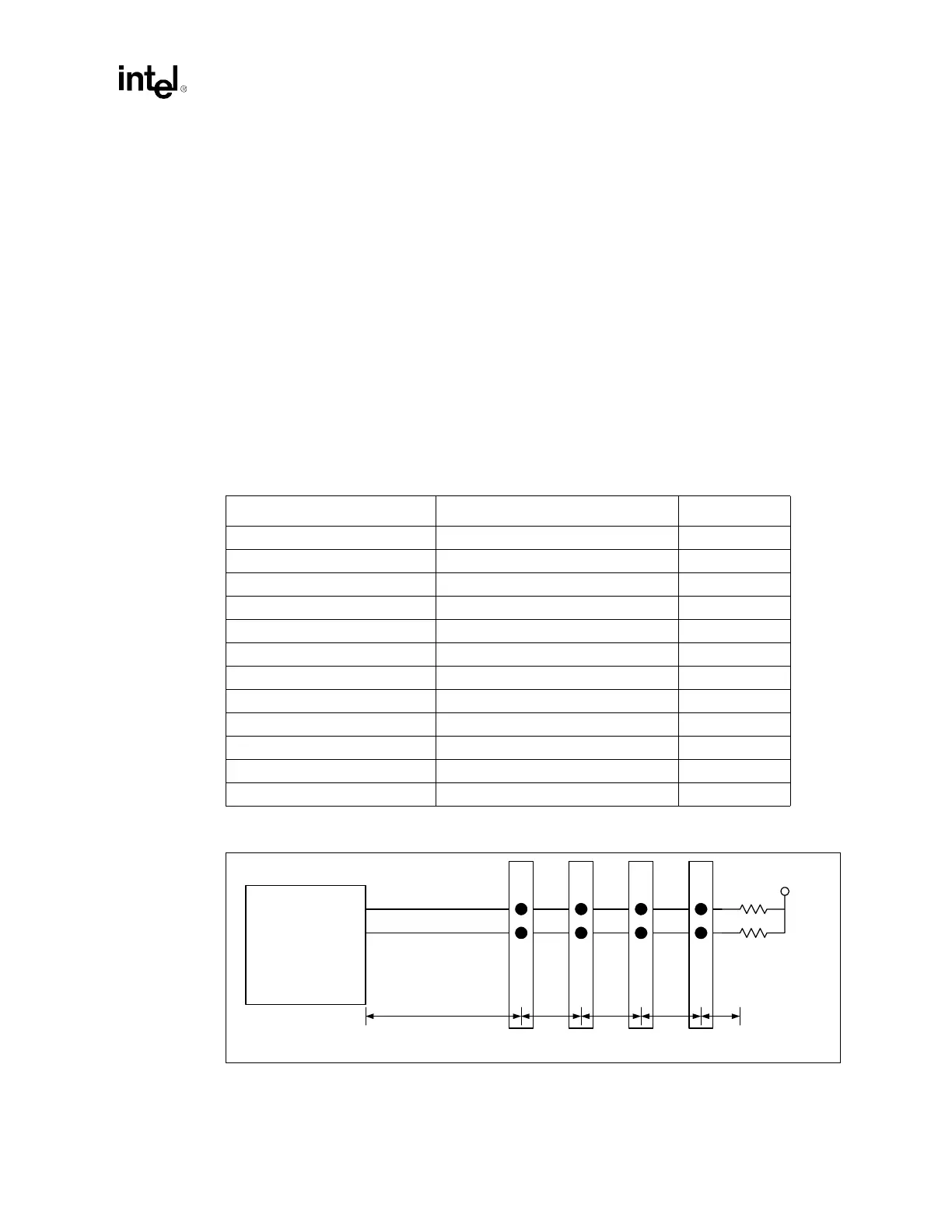

6.4 Source Clocked Signal Group Routing

The MCH drives the command clock signals required by the DDR interface; therefore, no external

clock driver is required for the DDR interface. The source-clocked signals are “clocked” into the

DIMMs using the command clock signals. Because the MCH drives the command clock signals

and the source-clocked signals together, these signals can be source clocked. That is, the MCH

drives the command clock in the center of the valid window, and the source-clocked signals

propagate with the command clock signal. Therefore, the critical timing is the difference between

the command clock flight time and the source clocked signal flight time. The absolute flight time is

not as critical.

The source-clocked signals have a topology similar to the source synchronous signals. These

signals require parallel termination resistors (Rtt) to DDR VTERM. The MCH requires matching

the lengths of the source-clocked signals to the lengths of the command clocks for each DIMM

within 2.0 inches. For example, if CMDCLK0 and CMDCLK0# are 3 inches long, all source

clocked signals from MCH to the DIMM that CMDCLK0/CMDCLK0# is routed to should be 3

inches ± 2.0 inches.

f

NOTE: Indicated lengths measure from the MCH pin to the DIMM connector pin.

Table 6-5. Source Clocked Signal Group Routing Guidelines

Parameter Intel

®

E7500 Reference

Signal Group RAS#, CAS#, WE#, MA[12:0], BA[1:0]

Topology Daisy Chain Figure 6-10

Reference Plane Ground Figure 6-3

Trace Impedance (Zo) 50

Ω ± 10% Figure 6-3

Nominal Trace Width 5 mil Figure 6-3

Nominal Trace Spacing 15 mil Figure 6-3

Trace Length – MCH to DIMM1 1.8” to 6.0” Figure 6-10

Trace Length – DIMM to DIMM 0.8” to 1.2” Figure 6-10

Trace Length – DIMM to Rtt < 0.8” Figure 6-10

Termination Resistor (Rtt) 22

Ω ± 2% Figure 6-10

MCH Breakout Guidelines 5/5, < 500 mil

Length Tuning Requirements To CMDCLK pair: ± 2.0” Figure 6-9

Figure 6-10. Source Clocked Signal Topology

DIMMs

MCH

RAS#, CAS#, WE#

MA[12:0], BA[1:0]

DDR VTERM

(1.25V)

MCH to DIMM1

DIMM to

DIMM

Rtt

Rtt

DIMM to

DIMM

DIMM to

DIMM

DIMM

to Rtt

Loading...

Loading...