Design Guide 17

Introduction

1.2 Conventions and Terminology

This section defines conventions and terminology used throughout the design guide.

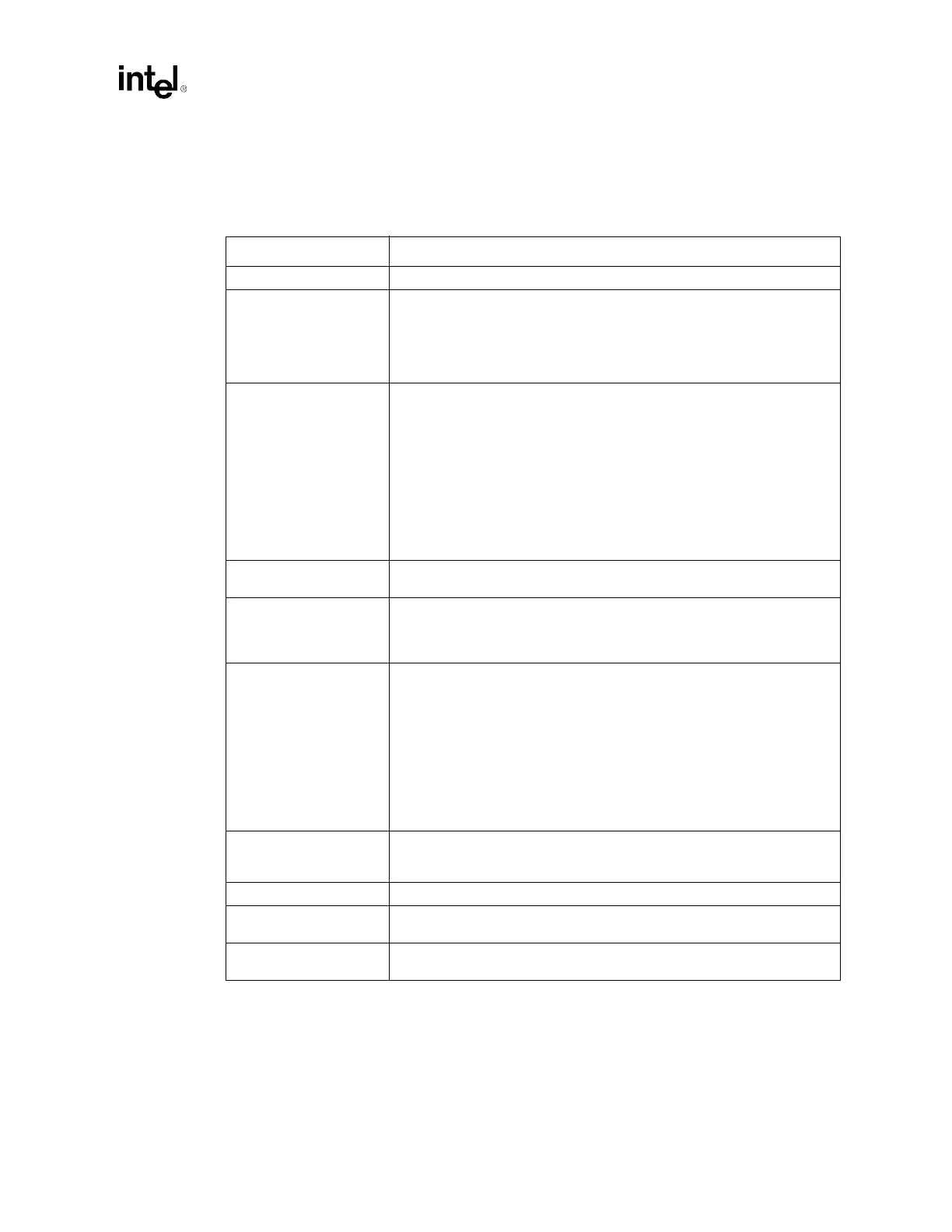

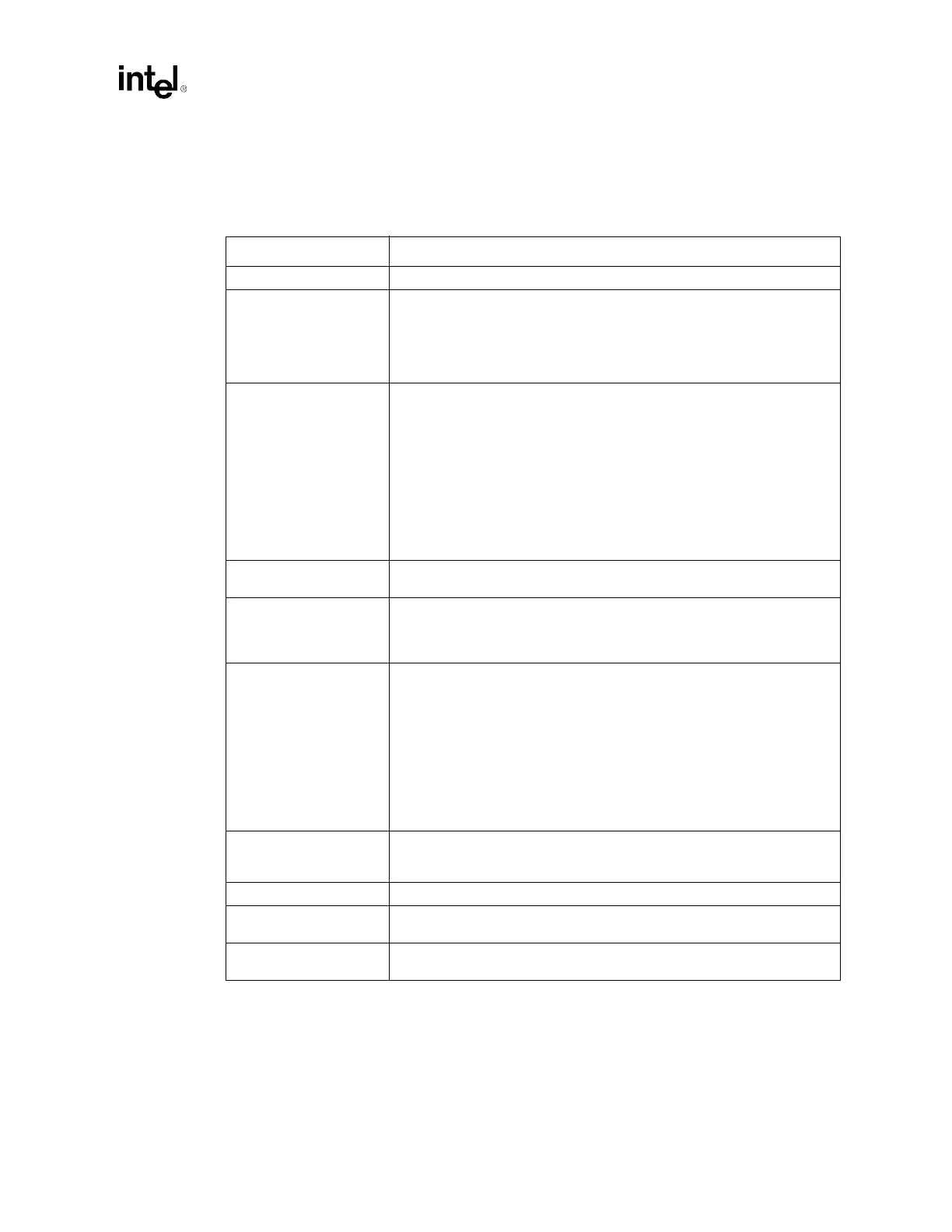

Convention/Terminology Description

Aggressor A network that transmits a coupled signal to another network.

AGTL+ The Xeon™ processor family system bus uses a bus technology called AGTL+,

or Assisted Gunning Transceiver Logic. AGTL+ buffers are open-drain, and

require pull-up resistors to provide the high logic level and termination. AGTL+

output buffers differ from GTL+ buffers with the addition of an active pMOS pull-

up transistor to assist the pull-up resistors during the first clock of a low-to-high

voltage transition.

Asynchronous GTL+ Xeon processors do not utilize CMOS voltage levels on any signals that connect

to the processor. As a result, legacy input signals such as A20M#, IGNNE#,

INIT#, LINT0/INTR, LINT1/NMI, PWRGOOD, SMI#, SLP#, and STPCLK# utilize

GTL+ input buffers. Legacy output signals (FERR# and IERR#) and non-AGTL+

signals (THERMTRIP# and PROCHOT#) also utilize GTL+ output buffers. All of

these signals follow the same DC requirements as AGTL+ signals, however the

outputs are not actively driven high (during a logical 0 to 1 transition) by the

processor (the major difference between GTL+ and AGTL+). These signals do

not have setup or hold time specifications in relation to BCLK[1:0], and are

therefore referred to as “Asynchronous GTL+ Signals”. However, all of the

Asynchronous GTL+ signals are required to be asserted for at least two BCLKs

in order for the processor to recognize them.

Bus Agent A component or group of components that, when combined, represent a single

load on the AGTL+ bus.

Core Power Core power refers to a power rail that is on only during full-power operation.

These power rails are on when the active-low PSON signal is asserted to the

power supply. The core power rails that are distributed directly from the power

supply are: +12 V, +5 V, and +3.3 V.

Crosstalk The reception on a victim network of a signal imposed by aggressor network(s)

through inductive and capacitive coupling between the networks.

• Backward Crosstalk – Coupling that creates a signal in a victim network that

travels in the opposite direction as the aggressor’s signal.

• Forward Crosstalk – Coupling that creates a signal in a victim network that

travels in the same direction as the aggressor’s signal.

• Even Mode Crosstalk – Coupling from a signal or multiple aggressors when

all the aggressors switch in the same direction that the victim is switching.

• Odd Mode Crosstalk – Coupling from a signal or multiple aggressors when

all the aggressors switch in the opposite direction that the victim is switching.

Derived power A derived power rail is any power rail that is generated from another power rail

using an on-board voltage regulator. For example, +2.5 V is derived from a +5 V

power rail using a voltage regulator.

Dual Processor (DP) Used to specify a system configuration using two processors.

Electromagnetic

Compatibility (EMC)

The successful operation of electronic equipment in its intended electromagnetic

environment.

Electromagnetic

Interference (EMI)

Electromagnetic radiation from an electrical source that interrupts the normal

function of an electronic device.

Loading...

Loading...