VTT_DDR

+V2_5

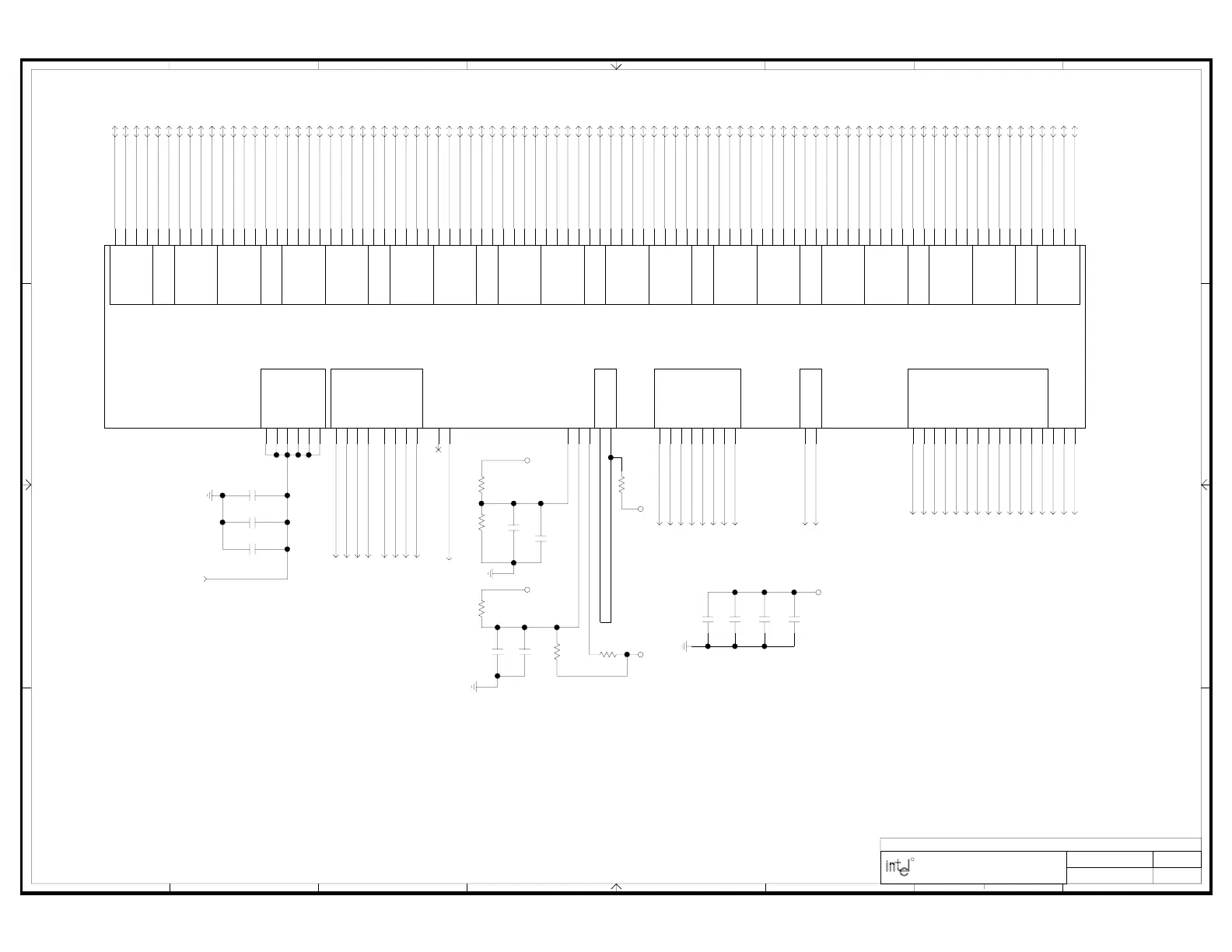

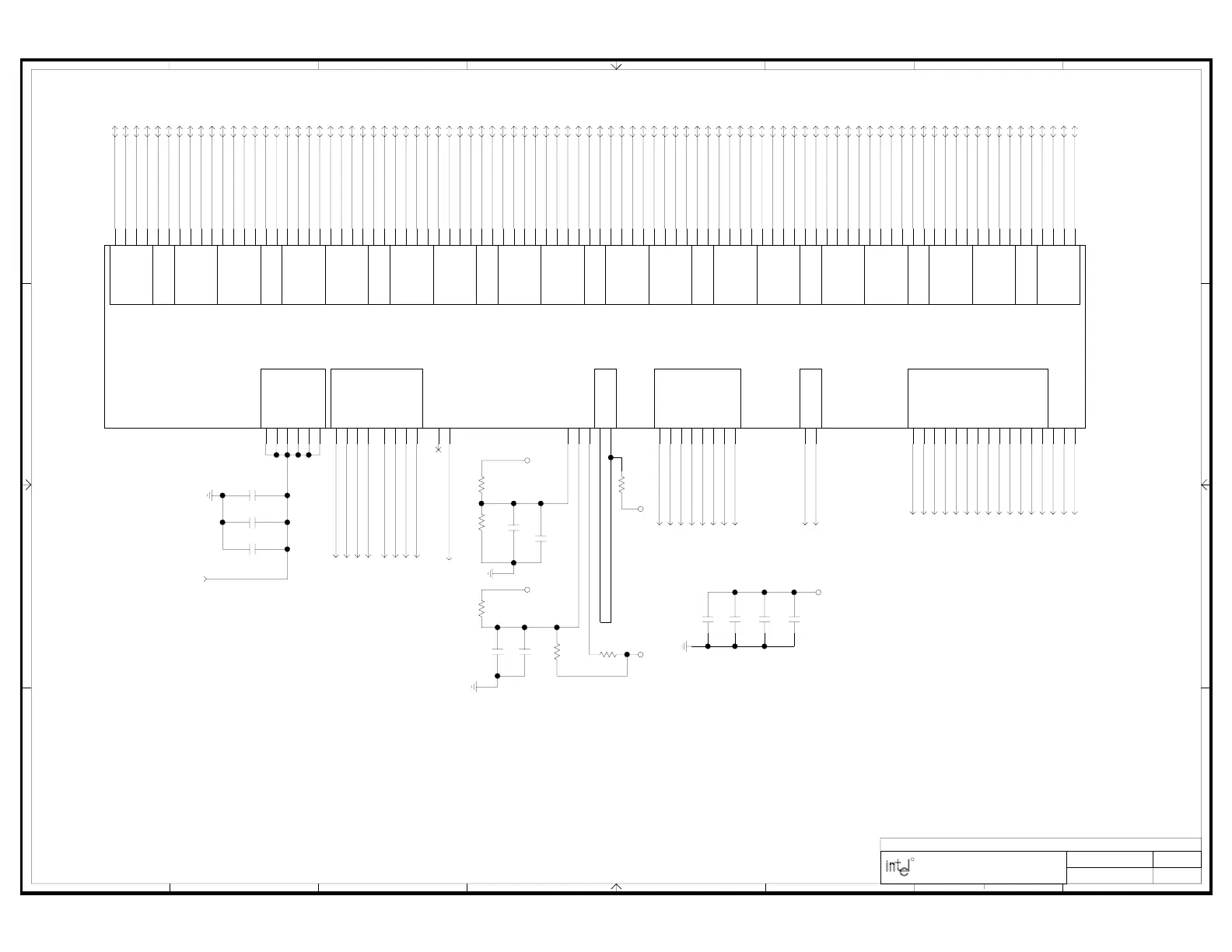

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

12345678

2345678

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

VTT_DDR

VTT_DDR VTT_DDR

DDRCVOL_A

DDRCVOH_A

DQ13_A

DQ16_A

DQ17_A

DQ18_A

DQ19_A

DQ22_A

CB7_A

DQ63_A

DQ61_A

DQ60_A

DQ59_A

DQ58_A

DQ57_A

DQ56_A

DQ55_A

DQ52_A

DQ51_A

DQ50_A

DQ49_A

DQ48_A

DQ47_A

DQ46_A

DQ45_A

DQ43_A

DQ42_A

DQ41_A

DQ40_A

DQ39_A

DQ38_A

DQ37_A

DQ36_A

DQ34_A

DQ33A

DQ32_A

DQ31_A

DQ30_A

DQ29_A

DQ28_A

DQ27_A

DQ26_A

DQ25_A

DQ24_A

DQ23_A

DQ21_A

DQ20_A

DQ9_A

DQ8_A

DQ7_A

DQ6_A

DQ5_A

DQ4_A

DQ2_A

DQ1_A

CB6_A

CB5_A

CB4_A

CB3_A

CB2_A

CB1_A

CB0_A

DQS17_A

DQS7_A

DQS6_A

DQS15_A

DQS5_A

DQS4_A

DQS13_A

DQS3_A

DQS12_A

DQS11A

DQS10_A

DQS0_A

DQS9_A

DQS1_A

DQS16_A

WE_N_A

CAS_N_A

RAS_N_A

MA0_A

MA4_A

MA5_A

MA7_A

MA6_A

MA8_A

MA9_A

MA11_A

MA12_A

BA1_A

BA0_A

CS7_N_A

CS4_N_A

CS3_N_A

CS2_N_A

CS1_N_A

RCVEN_OUT_A

RCVEN_IN_A

RESERVED

CMDCLK3_A

CMDCLK2_A

CMDCLK2_N_A

CMDCLK1_N_A

CMDCLK0_A

CMDCLK0_N_A

DDRVREF5_A

DDRVREF4_A

DDRVREF3_A

DDRVREF2_A

DDRVREF1_A

DQ12_A

DQ15_A

DQ53_A

DQ54_A

DQ62_A

DQ44_A

MA3_A

CKE_A

CMDCLK1_A

DDRVREF0_A

DQ0_A

MA10_A

MA1_A

MA2_A

DQS8_A

CMDCLK3_N_A

CS6_N_A

CS5_N_A

CS0_N_A

DQ3_A

DQ35_A

DQS2_A

DQS14_A

DDRCOMP_A

DQ10_A

DQ11_A

DQ14_A

Address Bus

MCH DDR A

Check BitsCheck Bits

Low NibbleHigh NibbleLow NibbleHigh NibbleLow NibbleHigh NibbleHigh Nibble Low Nibble High Nibble Low Nibble High Nibble Low Nibble Low Nibble High Nibble Low Nibble High Nibble Low Nibble

Chip Select

Command ClockVoltage Ref

Data Group 0Data Group 0Data Group 1Data Group 1Data Group 2Data Group 2Data Group 3Data Group 3Data Group 4Data Group 4Data Group 5

High Nibble

Data Group 5Data Group 6Data Group 6Data Group 7Data Group 7

MCH DDR Channel A

RCV_EN loop should be 15 inches total route

DDRA_RCV_EN

AN16

AK17

AK24

AK19

AL19

AN17

AF18

AL17

AG15

AM4

AE11

AH10

AM2

AM3

AJ9

AG10

AM6

AG12

AN5

AG11

AH11

AE12

AM10

AJ12

AF13

AL11

AN12

AH13

AE14

AG14

AH14

AN13

AK14

AJ15

AM13

AL14

AJ19

AN21

AJ21

AH20

AL20

AM21

AH19

AF19

AJ18

AM19

AN20

AM24

AN25

AL25

AL26

AM28

AN29

AE21

AN28

AM15

AG17

AE17

AK15

AL16

AH16

AE16

AF16

AL6

AL8

AM7

AM12

AL13

AJ13

AE18

AK20

AK18

AK23

AM27

AF21

AL23

AH9

AE23

AE22

AN24

AF24

AG27

AH28

AL29

AL28

AK29

AM30

AK30

AM31

AH23

AL31

AL2

AN8

AH8

AL10

AK11

AG20

AM22

AM18

AE25

AG26

AF25

AH25

AG24

AG23

AJ28

AK27

AK21

AM16

AL9

AM25

AJ22

AF12

AM9

AL5

AE15

AJ27

AE19

AJ25

AJ7

AF22

AJ24

AK26

AH26

AJ16

AE24

AL3

AK7

AE13

AH22

AF15

AG18

AK12

AH17

AG21

AE20

AL22

U66

DDRA_CKE0

16-20

VREF_DDR_MCH

13,62

0.1UF

C1667

C1666

0.01UF

C780

0.1UF

0.01UF

C779

19

DDRA_CMDCLK3

19

DDRA_CMDCLK3_N

18

DDRA_CMDCLK2

18

DDRA_CMDCLK2_N

17

DDRA_CMDCLK1

17

DDRA_CMDCLK1_N

16

DDRA_CMDCLK0

16

DDRA_CMDCLK0_N

R115

6.81

C1145

0.1UF

0.1UF

C1144

C1143

0.1UF

0.1UF

C777

6.98K

1%

R524

6.98K

1%

R523

DDRA_DRCOMP

DDRA_MA12_R

16-20

DDRA_MA11_R

16-20

DDRA_MA10_R

16-20

DDRA_MA9_R

16-20

DDRA_MA8_R

16-20

DDRA_MA7_R

16-20

DDRA_MA6_R

16-20

DDRA_MA5_R

16-20

DDRA_MA4_R

16-20

DDRA_MA3_R

16-20

DDRA_MA2_R

16-20

DDRA_MA1_R

16-20

DDRA_MA0_R

16-20

DDRA_RAS_N_R

16-20

DDRA_CAS_N_R

16-20

DDRA_WE_N_R

16-20

DDRA_DQ34

15

DDRA_DQ33

15

DDRA_DQ30

15

DDRA_DQ29

15

DDRA_DQS12

15

DDRA_DQ26

15

DDRA_DQ25

15

15

DDRA_DQ23

DDRA_DQ22

15

DDRA_DQ21

15

DDRA_DQS11

15

DDRA_DQ18

15

DDRA_DQ17

15

DDRA_DQ14

15

DDRA_DQ13

15

DDRA_DQS10

15

DDRA_DQ9

15

DDRA_DQ6

15

DDRA_DQ5

15

DDRA_DQS9

15

DDRA_DQ2

15

DDRA_DQ1

15

15

DDRA_DQ3

DDRA_DQ0

15

15

DDRA_DQ7

DDRA_DQ4

15

15

DDRA_DQ10

DDRA_DQ8

15

15

DDRA_DQ15

DDRA_DQ12

15

15

DDRA_DQ19

DDRA_DQ16

15

DDRA_DQ20

15

15

DDRA_DQ27

DDRA_DQ24

15

15

DDRA_DQ31

DDRA_DQ28

15

15

DDRA_DQ35

DDRA_DQ32

15

DDRA_DQS13

15

DDRA_DQ37

15

DDRA_DQ38

15

15

DDRA_DQ39

DDRA_DQ36

15

DDRA_DQ41

15

DDRA_DQ42

15

15

DDRA_DQ43

DDRA_DQ40

15

DDRA_DQS14

15

15

DDRA_DQ44

15

DDRA_DQ46

DDRA_DQ45

15

DDRA_DQ49

15

DDRA_DQ50

15

15

DDRA_DQ51

DDRA_DQ48

15

DDRA_DQS15

15

DDRA_DQ53

15

15

DDRA_DQ54

DDRA_DQ52

15

DDRA_DQ56

15

DDRA_DQ57

15

DDRA_DQ59

15

15

DDRA_DQ58

DDRA_DQ60

15

DDRA_DQS16

15

DDRA_DQ61

15

15

DDRA_DQ62

DDRA_CB1

15

15

DDRA_CB2

DDRA_CB3

15

DDRA_CB0

15

DDRA_CB4

15

15

DDRA_CB5

15

DDRA_CB7

DDRA_CB6

15

R841

47

DDRCVOH_A

DDRA_CS0_N_R

16,20

DDRA_CS1_N_R

16,20

DDRA_CS2_N_R

17,20

DDRA_CS3_N_R

17,20

DDRA_CS4_N_R

18,26

DDRA_CS5_N_R

18,26

DDRA_CS6_N_R

19,20

DDRA_CS7_N_R

19,20

DDRA_DQS7

15

DDRA_DQS17

15

DDRA_BA0_R

16-20

DDRA_BA1_R

16-19,26

DDRA_DQS0

15

DDRA_DQS1

15

DDRA_DQS2

15

DDRA_DQS3

15

DDRA_DQS4

15

DDRA_DQS5

15

DDRA_DQS6

15

DDRA_DQS8

15

R522

13K

C778

0.01UF

13K

R521

DDRCVOL_A

DDRA_DQ63

15

DDRA_DQ55

15

DDRA_DQ47

15

DDRA_DQ11

15

0.01UF

C1668

C1669

0.1UF

12

Loading...

Loading...