dsPIC30F Family Reference Manual

DS70070B-page 23-16 © 2004 Microchip Technology Inc.

23.2.6 CAN Baud Rate Registers

This subsection describes the CAN baud rate registers.

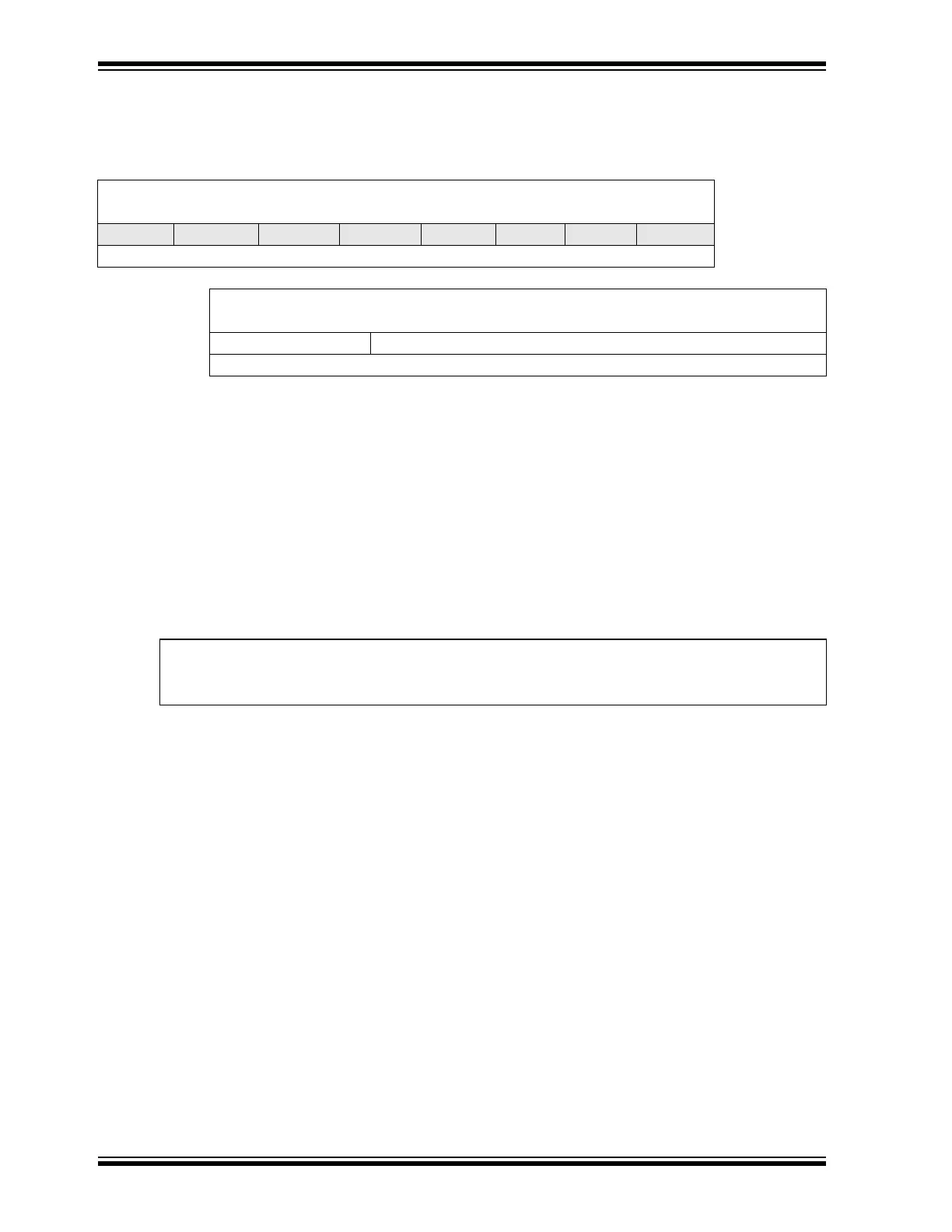

Register 23-19: CiCFG1: Baud Rate Configuration Register 1

Upper Byte:

U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

bit 15 bit 8

Lower Byte:

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

SJW<1:0> BRP<5:0>

bit 7 bit 0

bit 15-8 Unimplemented: Read as ‘0’

bit 7-6 SJW<1:0>: Synchronized Jump Width bits

11 = Synchronized jump width time is 4 x T

Q

10 = Synchronized jump width time is 3 x TQ

01 = Synchronized jump width time is 2 x TQ

00 = Synchronized jump width time is 1 x TQ

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

11 1111 = T

Q = 2 x (BRP + 1)/FCAN

= 128/FCAN

.

.

00 0000 = T

Q = 2 x (BRP + 1)/FCAN

= 2/FCAN

Note: FCAN

is FCY or 4 FCY, depending on the CANCKS bit setting.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

Loading...

Loading...