© 2004 Microchip Technology Inc. DS70070B-page 23-19

Section 23. CAN

CAN Module

23

23.2.8 CAN Interrupt Registers

This subsection documents the CAN Registers which are associated with interrupts.

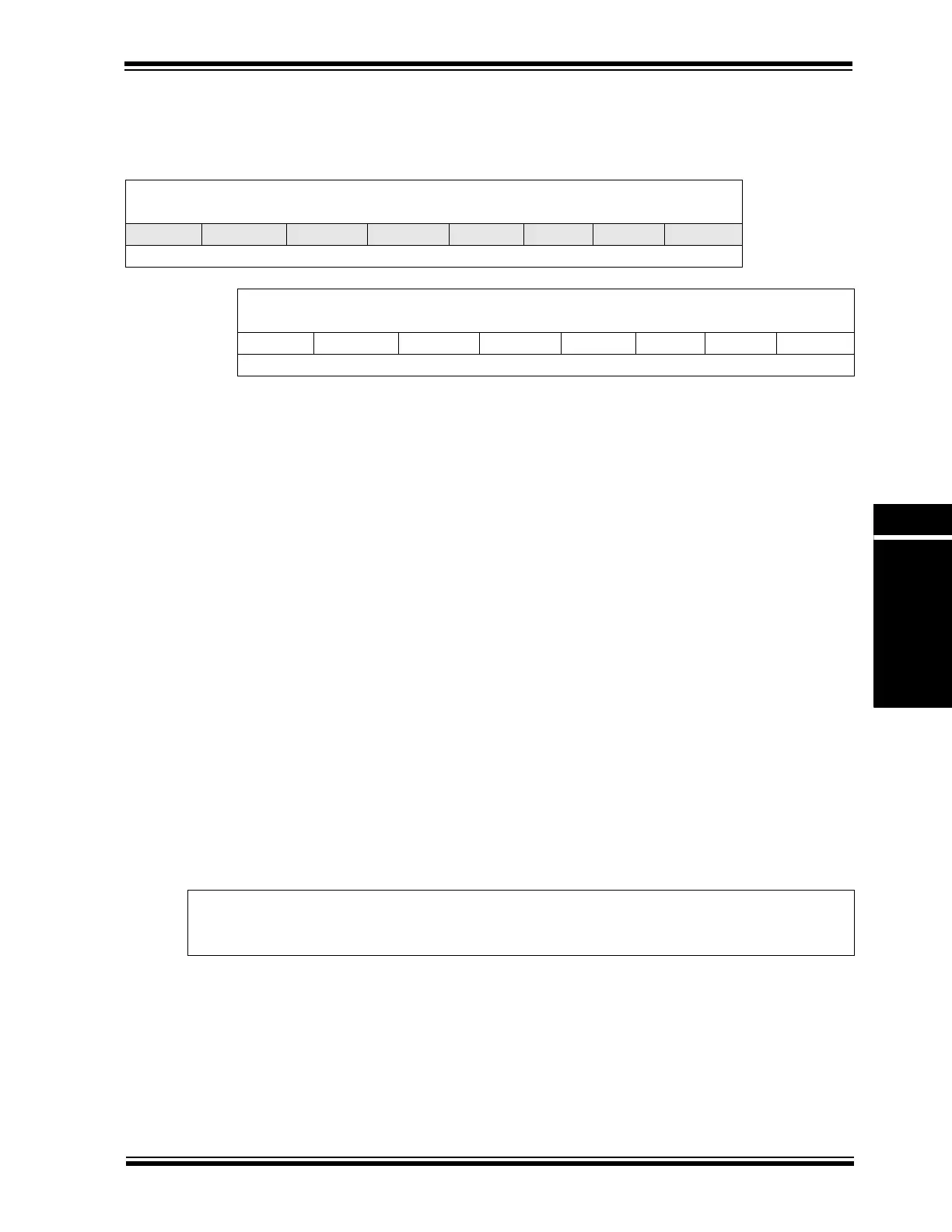

Register 23-22: CiINTE: Interrupt Enable Register

Upper Byte:

U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0

— — — — — — — —

bit 15 bit 8

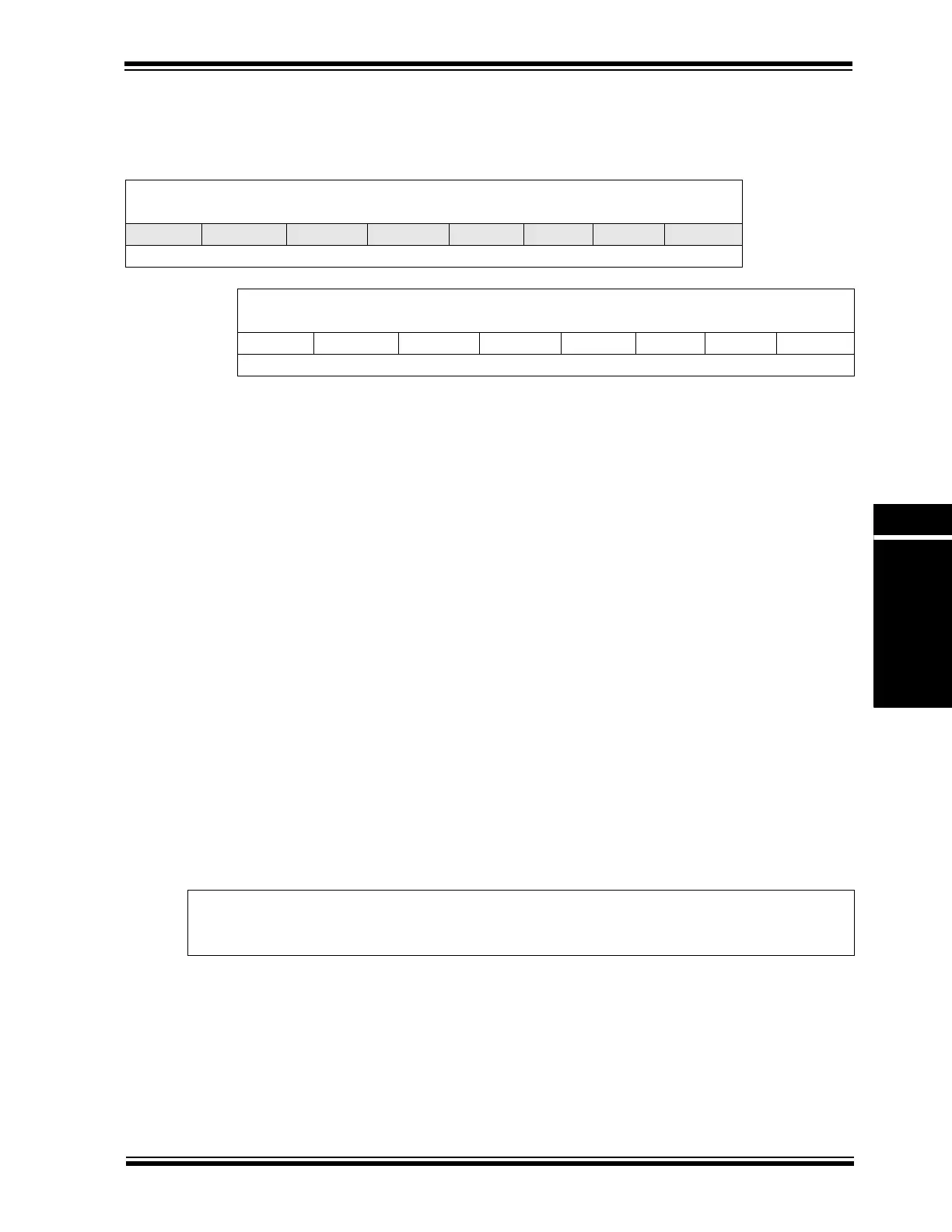

Lower Byte:

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

IVRIE WAKIE ERRIE TX2IE TX1IE TX0IE RX1IE RX0IE

bit 7 bit 0

bit 15-8 Unimplemented: Read as ‘0’

bit 7 IVRIE: Invalid Message Received Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 WAKIE: Bus Wake Up Activity Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 5 ERRIE: Error Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 4 TX2IE: Transmit Buffer 2 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 3 TX1IE: Transmit Buffer 1 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 2 TX0IE: Transmit Buffer 0 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 1 RX1IE: Receive Buffer 1 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 0 RX0IE: Receive Buffer 0 Interrupt Enable bit

1 = Enabled

0 = Disabled

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

Loading...

Loading...