RL78/G1H CHAPTER 14 SERIAL ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 403 of 920

Dec 22, 2016

Note When changing the clock selected for fCLK (by changing the system clock control register (CKC) value), do so after

having stopped (serial channel stop register m (STm) = 000FH) the operation of the serial array unit (SAU).

Remark ×: Don’t care

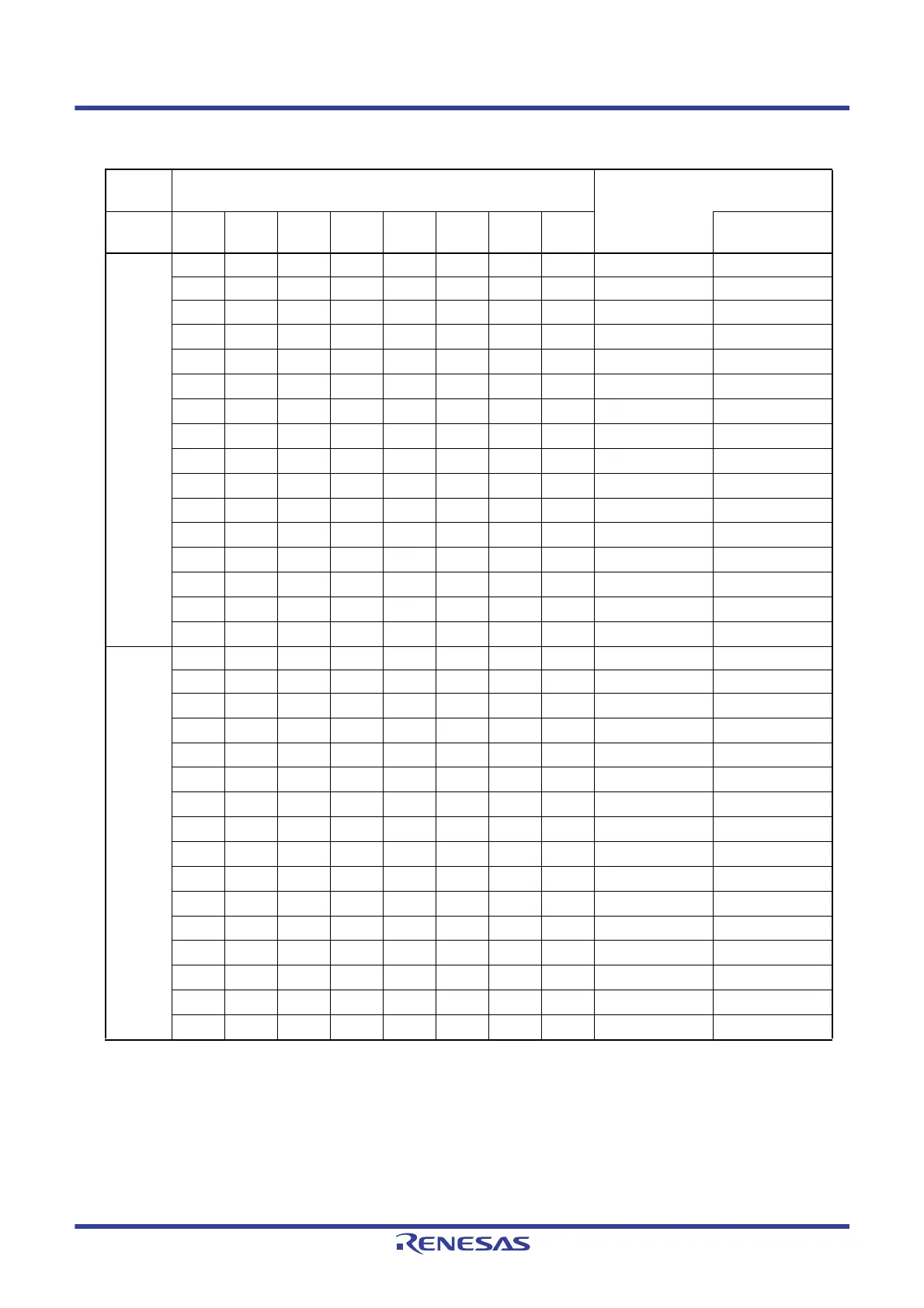

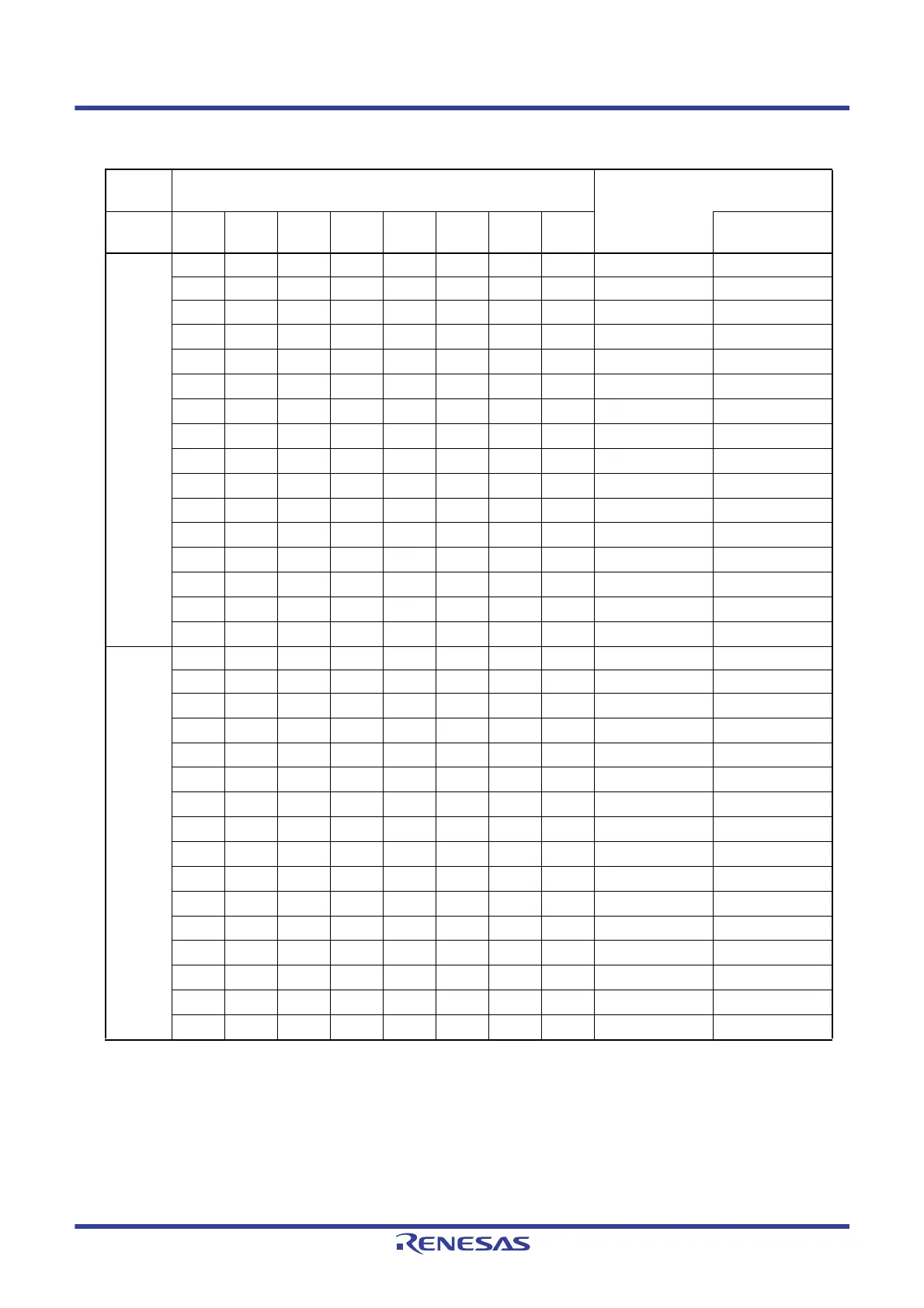

Table 14 - 2 Selection of Operation Clock For 3-Wire Serial I/O

SMRmn

Register

SPSm Register

Operation Clock (f

MCK)

Note

CKSmn

PRS

m13

PRS

m12

PRS

m11

PRS

m10

PRS

m03

PRS

m02

PRS

m01

PRS

m00

fCLK = 32 MHz

0

××××0000 fCLK 32 MHz

××××0001 fCLK/2 16 MHz

××××0010

f

CLK/2

2

8 MHz

××××0011

f

CLK/2

3

4 MHz

××××0100

f

CLK/2

4

2 MHz

××××0101

f

CLK/2

5

1 MHz

××××0110

f

CLK/2

6

500 kHz

××××0111

f

CLK/2

7

250 kHz

××××1000

f

CLK/2

8

125 kHz

××××1001

f

CLK/2

9

62.5 kHz

××××1010

f

CLK/2

10

31.25 kHz

××××1011

f

CLK/2

11

15.63 kHz

××××1100

f

CLK/2

12

7.81 kHz

××××1101

f

CLK/2

13

3.91 kHz

××××1110

f

CLK/2

14

1.95 kHz

××××1111

f

CLK/2

15

977 Hz

1 0000

×××× fCLK 32 MHz

0001

×××× fCLK/2 16 MHz

0010

××××

fCLK/2

2

8 MHz

0011

××××

fCLK/2

3

4 MHz

0100

××××

fCLK/2

4

2 MHz

0101

××××

fCLK/2

5

1 MHz

0110

××××

fCLK/2

6

500 kHz

0111

××××

fCLK/2

7

250 kHz

1000

××××

fCLK/2

8

125 kHz

1001

××××

fCLK/2

9

62.5 kHz

1010

××××

fCLK/2

10

31.25 kHz

1011

××××

fCLK/2

11

15.63 kHz

1100

××××

fCLK/2

12

7.81 kHz

1101

××××

fCLK/2

13

3.91 kHz

1110

××××

fCLK/2

14

1.95 kHz

1111

××××

fCLK/2

15

977 Hz

Loading...

Loading...