RL78/G1H CHAPTER 18 RF TRANSCEIVER

R01UH0575EJ0120 Rev. 1.20 Page 573 of 920

Dec 22, 2016

(8) Transmit/receive mode register 2 (BBTXRXMODE2)

This register sets the various types of the RF transmit/receive mode.

The automatic CRC disable bit can be used to select between to transmit with the CRC calculation result

automatically attached upon transmit, and to transmit the data on the RAM.

The frame pending bit can be used to set with/without the frame pending upon ACK reply when the address

matches on the first address side. Information on this bit is automatically included in the ACK replay data.

The frame pending status bit is used to display whether the reply is made with frame pending or not upon

the automatic ACK reply. The display is updated at the same time of the occurrence of interrupt request

upon completion of the transmission. The information on the frame pending upon reply by the save bank

which is selected by the receive data save bank select bit is read upon reading because this bit left the

result of the automatic ACK reply for every received save bank.

The enhanced ACK enable bit can be used to support the enhanced ACK reply function.

It can be used to set the number of retransmission times by using the retransmission counter when there is

no ACK reply even if the automatic ACK receive mode is enabled. The value ranged from 0000b through

1000b can be set.

The BBTXRXMODE2 register is set by the serial interface in 8-bit units.

Reset signal generation sets this register to 30H.

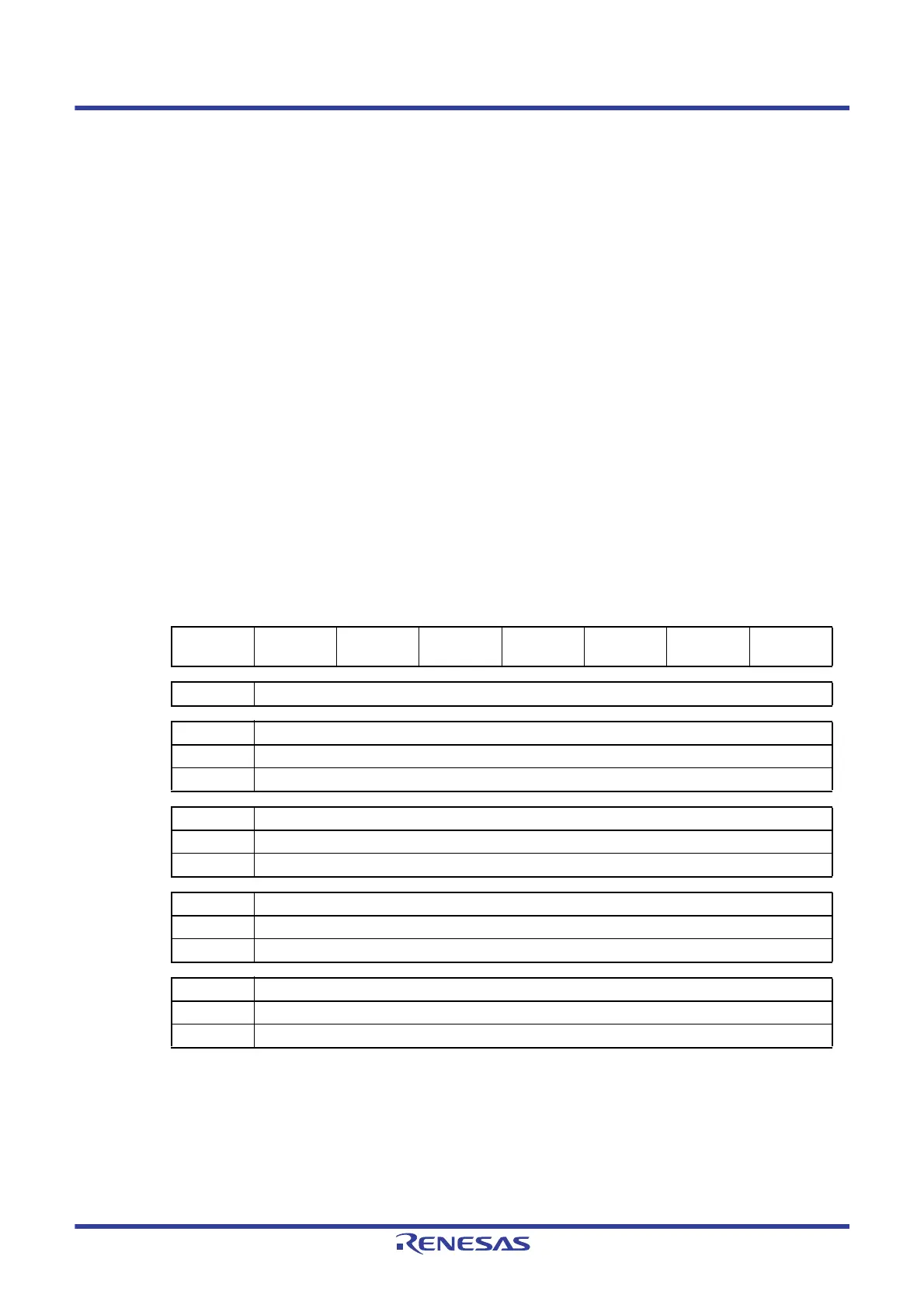

Figure 18 - 14 Transmit/Receive Mode Register 2 (BBTXRXMODE2) Format

Note Bit 2 is Read Only.

Address:

0009H

After reset:

30H

R/W

Note

Symbol76543210

BBTXRX

MODE2

RETRN3 RETRN2 RETRN1 RETRN0 ENHACKEN FLMPENDST FLMPEND NOCRC

RETRN[3:0] Retransmission counter (From 0000B up to 1000B can be set.)

ENHACKEN Enhanced ACK Enable bit

0 Enhanced ACK disabled

1 Enhanced ACK enabled

FLMPENDST

Frame pending status bit

0 No frame pending

1 Frame pending exists

FLMPEND Frame pending bit

0 No frame pending

1 Frame pending exists

NOCRC Automatic CRC enable bit

0 Enable

1 Disable

Loading...

Loading...