RL78/G1H CHAPTER 18 RF TRANSCEIVER

R01UH0575EJ0120 Rev. 1.20 Page 597 of 920

Dec 22, 2016

(29) Baseband interrupt enable register 0 (BBINTEN0)

This register is used to enable the baseband interrupt.

This register enables the interrupt output from the INTOUT pin upon generation of each interrupt. Set “1” to

the corresponding interrupt enable bit when you want to enable the interrupt output.

The BBINTEN0 register consists of 8 bits and can be accessed (serial interface communication) in 8 bit unit.

Reset signal generation clears this register to 00H.

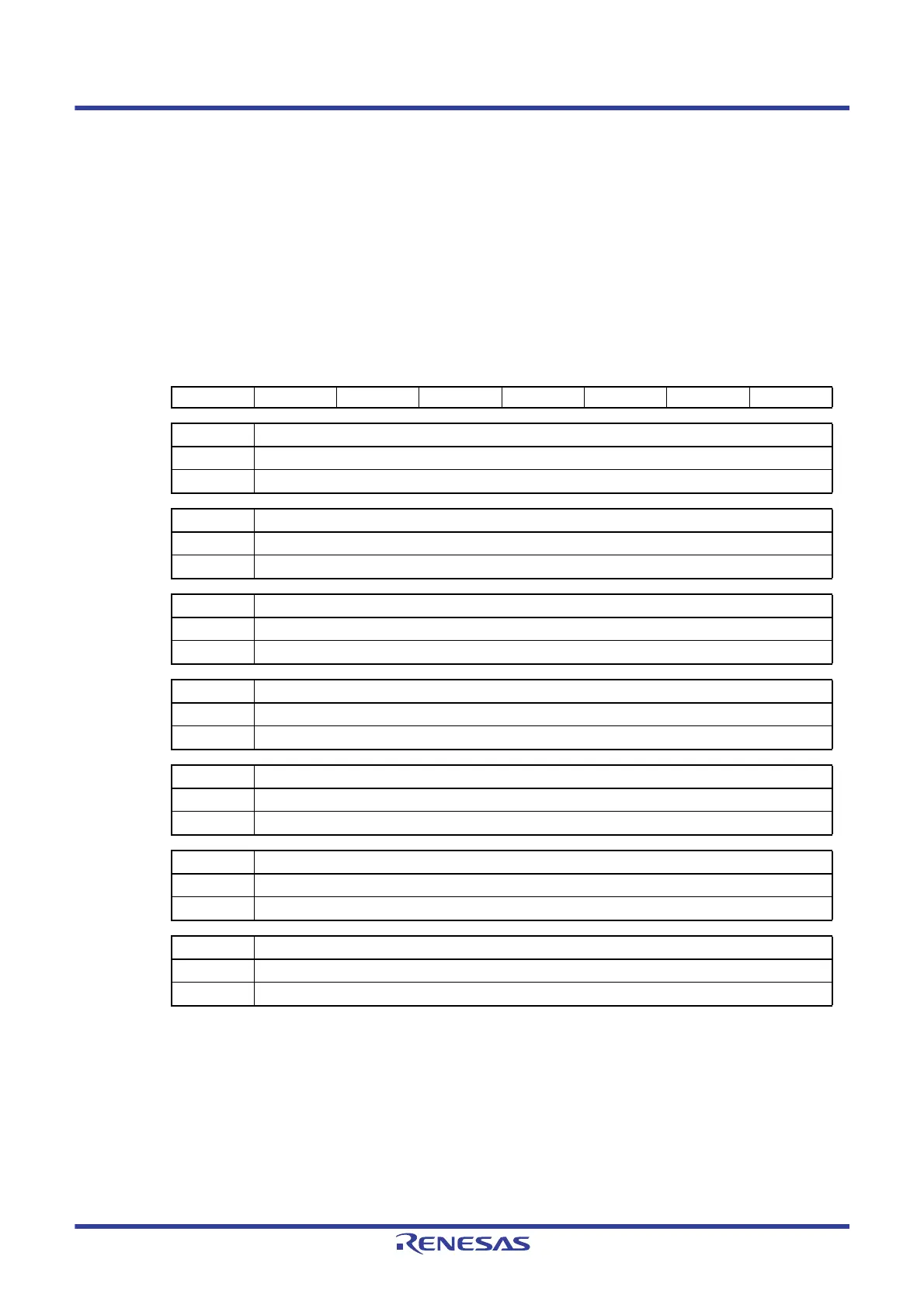

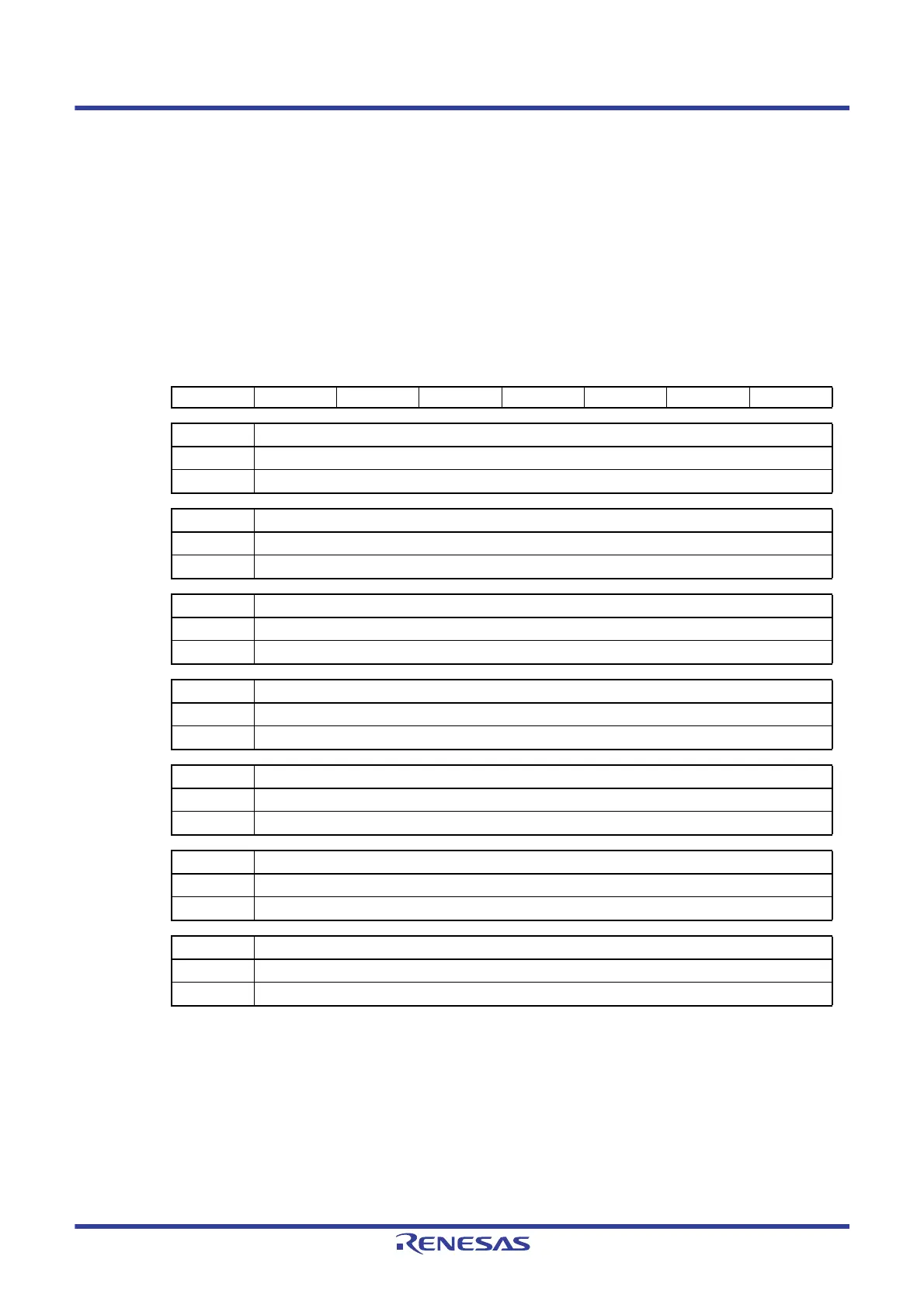

Figure 18 - 38 Baseband Interrupt Enable Register 0 (BBINTEN0) Format

Caution Be sure to clear bit 6 to "0". It is read as x (undefined).

Address:

0039H

After reset: 00H R/W

Symbol76543210

BBINTEN0

CCAINTEN X TRN1INTEN TRN0INTEN

TRNFININTEN

TIM2INTEN TIM1INTEN TIM0INTEN

CCAINTEN CCA completion interrupt enable bit

0 Disabled

1 Enabled

TRN1INTEN Bank 1 transmit completion interrupt enable bit

0 Disabled

1 Enabled

TRN0INTEN Bank 0 transmit completion interrupt enable bit

0 Disabled

1 Enabled

TRNFININTEN

Frame transmit completion interrupt cause bit

0 Disabled

1 Enabled

TIM2INTEN Timer compare 2 interrupt enable bit

0 Disabled

1 Enabled

TIM1INTEN Timer compare 1 interrupt enable bit

0 Disabled

1 Enabled

TIM0INTEN Timer compare 0 interrupt enable bit

0 Disabled

1 Enabled

Loading...

Loading...