RL78/G1H CHAPTER 20 STANDBY FUNCTION

R01UH0575EJ0120 Rev. 1.20 Page 737 of 920

Dec 22, 2016

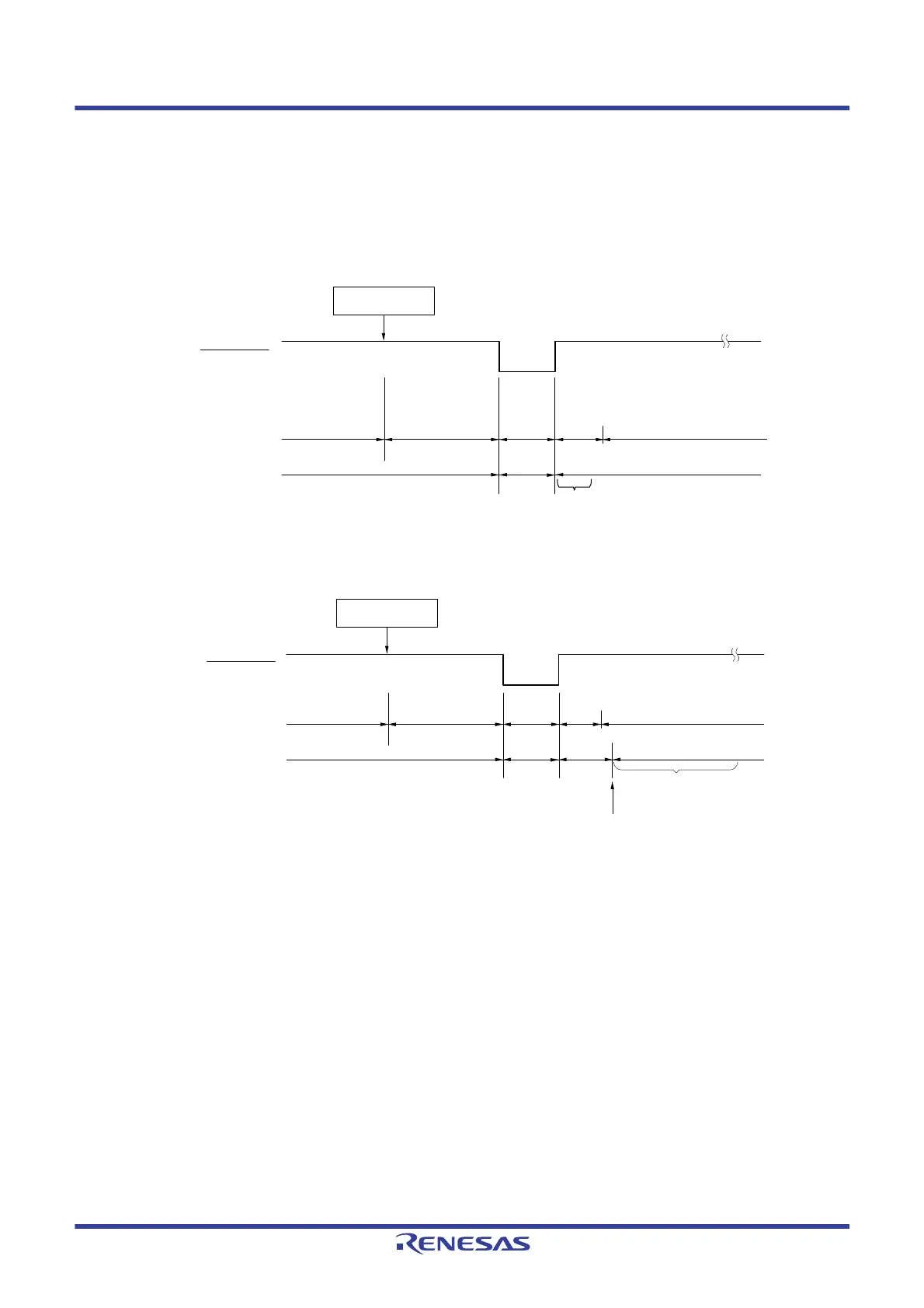

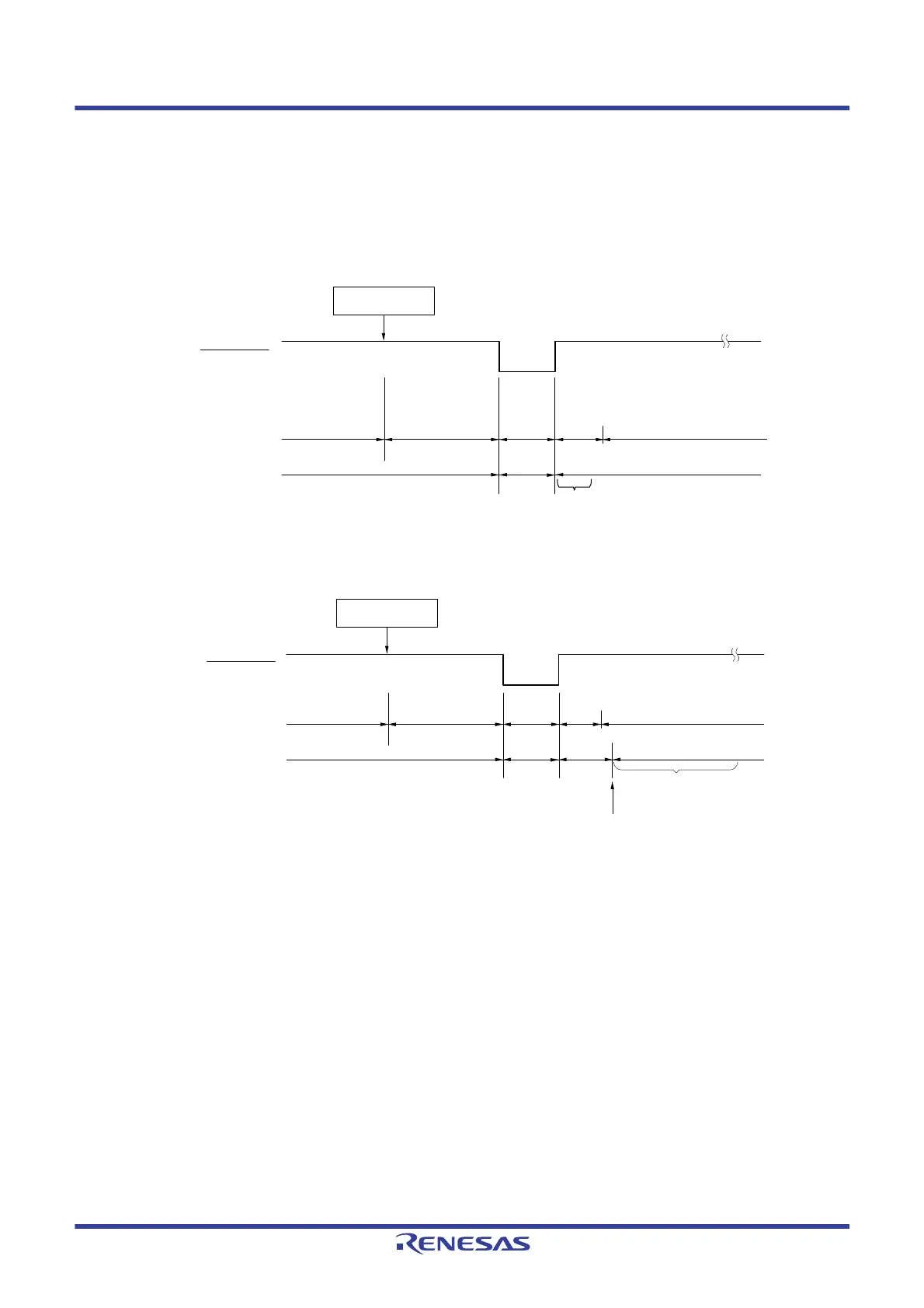

(b) Release by reset signal generation

When the reset signal is generated, HALT mode is released, and then, as in the case with a normal reset

operation, the program is executed after branching to the reset vector address.

Figure 20 - 2 HALT Mode Release by Reset (1/2)

(1) When high-speed on-chip oscillator clock is used as CPU clock

(2) When high-speed system clock is used as CPU clock

Note For the reset processing time, see CHAPTER 21 RESET FUNCTION.

HALT instruction

High-speed on-chip

oscillator clock

Oscillates

Oscillation

stopped

Oscillates

Wait for oscillation

accuracy stabilization

Status of CPU

Reset signal

Normal operation

(high-speed on-chip

oscillator clock)

HALT mode

Reset

period

Normal operation

(high-speed on-chip

oscillator clock)

Note

HALT instruction

High-speed system clock

(X1 oscillation)

Normal operation

(high-speed system clock)

HALT mode

Oscillates

Oscillation

stopped

Oscillates

Status of CPU

Oscillation

stopped

Reset signal

Reset

period

Normal operation

(high-speed on-chip

oscillator clock)

Starting X1 oscillation is specified by software.

Oscillation stabilization time

(check by using OSTC register)

Note

Loading...

Loading...