RL78/G1H CHAPTER 20 STANDBY FUNCTION

R01UH0575EJ0120 Rev. 1.20 Page 744 of 920

Dec 22, 2016

Remark Operation stopped: Operation is automatically stopped before switching to the STOP mode.

Operation disabled: Operation is stopped before switching to the STOP mode.

f

IH: High-speed on-chip oscillator clock fIL: Low-speed on-chip oscillator clock

f

X: X1 clock fEX: External main system clock

f

XT: XT1 clock fEXS: External subsystem clock

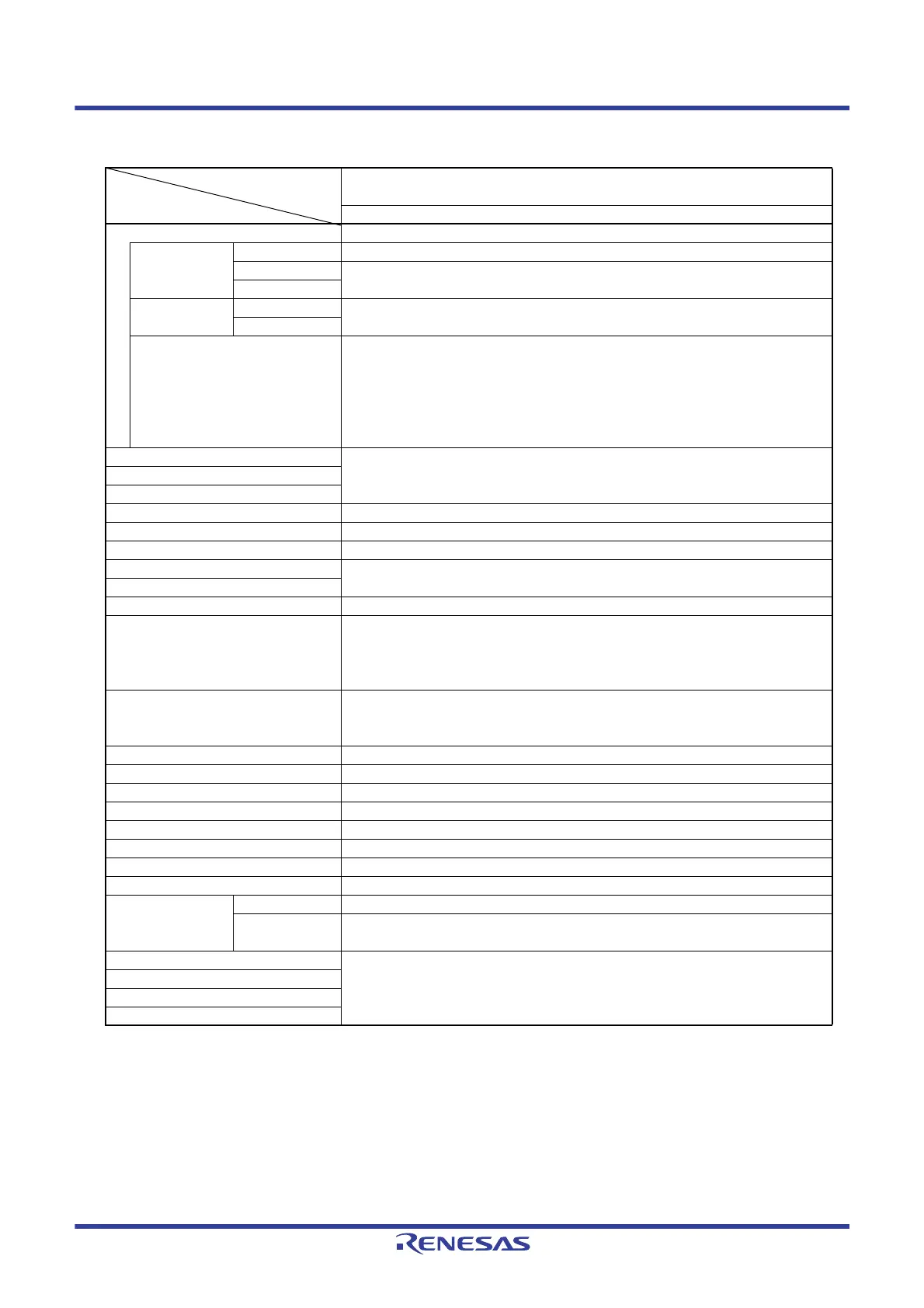

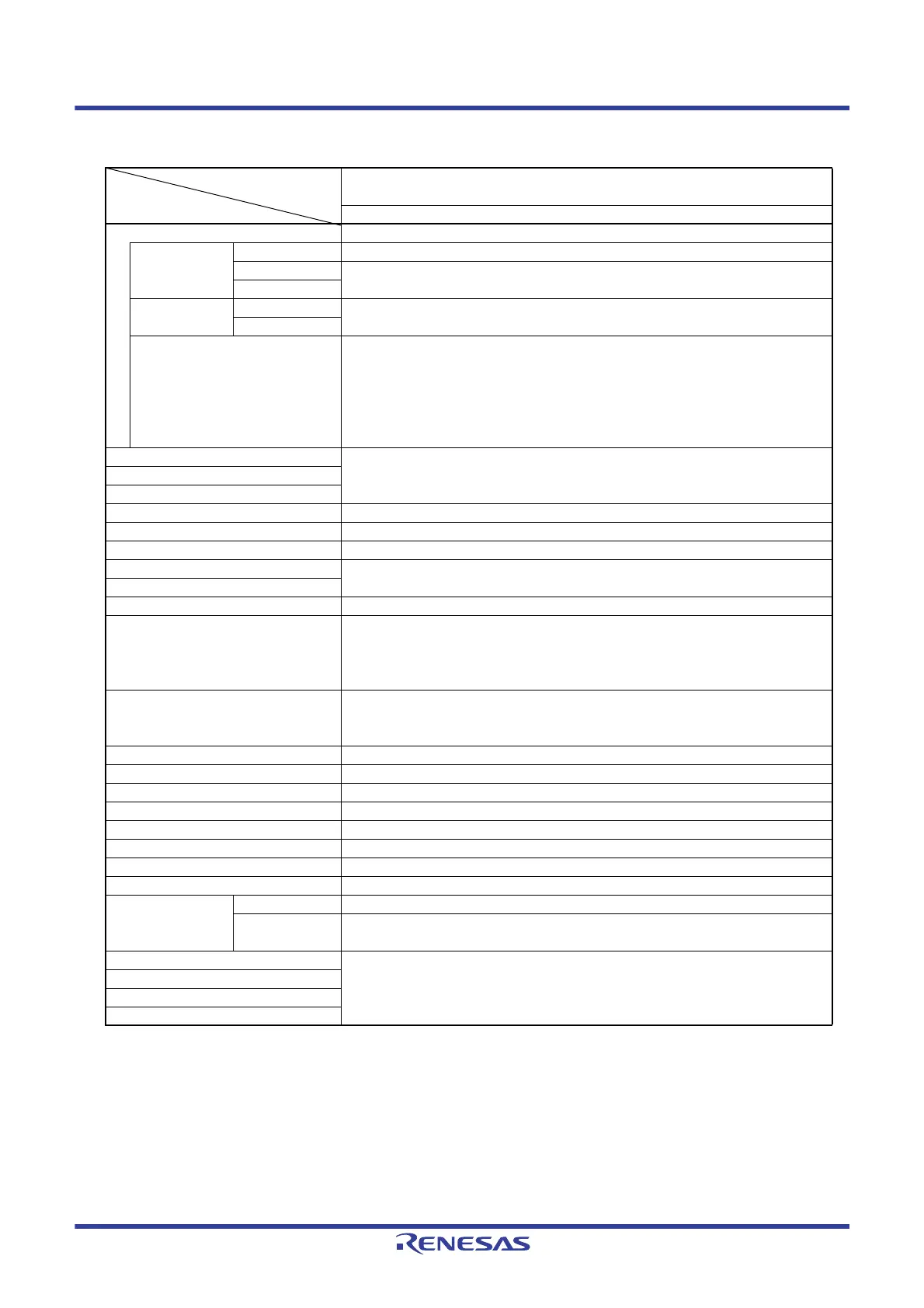

Table 20 - 4 Operating Statuses in SNOOZE Mode

STOP Mode Setting

Item

During STOP mode, receiving data signal from CSIp and UARTq, inputting timer trigger

signal to A/D converter, and generating DTC activation by interrupt

When CPU is Operating on High-speed On-chip Oscillator Clock (f

IH)

System clock Clock supply to the CPU is stopped

Main system

clock

f

IH Operation started

f

X Stopped

f

EX

Subsystem clock fXT Use of the status while in the STOP mode continues

f

EXS

fIL Set by bits 0 (WDSTBYON) and 4 (WDTON) of option byte (000C0H), and WUTMMCK0

bit of subsystem clock supply mode control register (OSMC)

• WUTMMCK0 = 1: Oscillates

• WUTMMCK0 = 0 and WDTON = 0: Stops

• WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 1: Oscillates

• WUTMMCK0 = 0, WDTON = 1, and WDSTBYON = 0: Stops

CPU Operation stopped

Code flash memory

Data flash memory

RAM Operation stopped (Operable while in the DTC is executed)

Port (latch) Use of the status while in the STOP mode continues

Timer array unit Operation disabled

Real-time clock (RTC) Operable

12-bit interval timer

Watchdog timer See

CHAPTER 12 WATCHDOG TIMER.

Timer RJ • Operable when the subsystem clock is selected as the count source and RTCLPC in

the OSMC register = 0

• Operable when the low-speed on-chip oscillator is selected as the count source

• Operation is disabled under any conditions other than the above

Clock output/buzzer output Operates when the subsystem clock is selected as the clock source for counting and the

RTCLPC bit is 0 (operation is disabled when a clock other than the subsystem clock is

selected and the RTCLPC bit is not 0).

A/D converter Operable

Serial array unit (SAU) Operation disabled

Serial interface (IICA) Operation disabled

Data transfer controller (DTC) Operable

Event link controller (ELC) Operable function blocks can be linked

Power-on-reset function Operable

Voltage detection function

External interrupt

CRC operation

function

High-speed CRC Operation stopped

General-purpose

CRC

Operation disabled

Illegal-memory access detection function Operable when executing the DTC

RAM parity error detection function

RAM guard function

SFR guard function

Loading...

Loading...