RL78/G1H CHAPTER 24 SAFETY FUNCTIONS

R01UH0575EJ0120 Rev. 1.20 Page 788 of 920

Dec 22, 2016

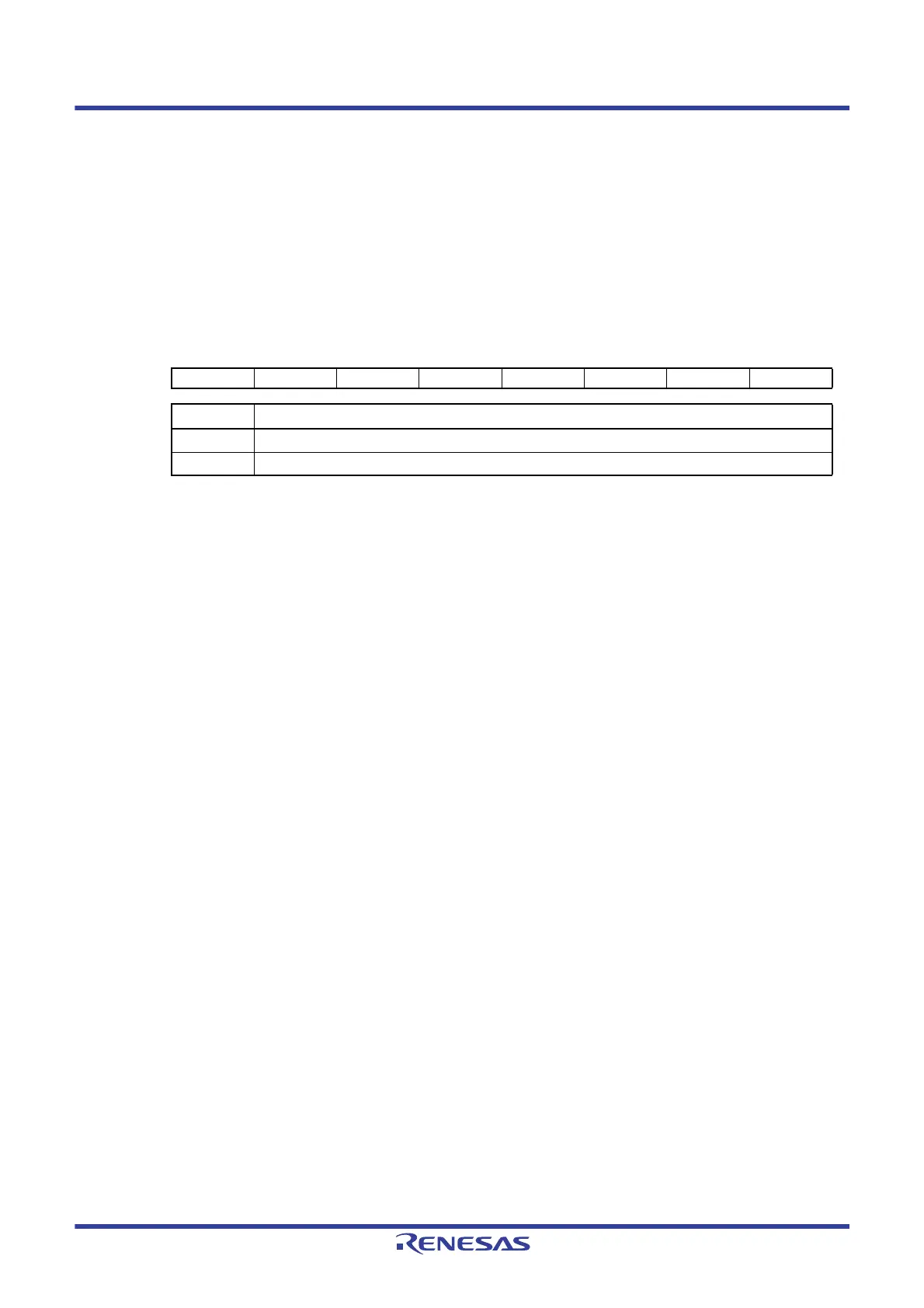

24.3.6.1 Invalid memory access detection control register (IAWCTL)

This register is used to control the detection of invalid memory access and RAM/SFR guard function.

IAWEN bit is used in invalid memory access detection function.

The IAWCTL register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

Figure 24 - 12 Format of Invalid memory access detection control register (IAWCTL)

Note Only writing 1 to the IAWEN bit is enabled, not writing 0 to it after setting it to 1.

Remark By specifying WDTON = 1 for the option byte (watchdog timer operation enable), the invalid memory access

detection function is enabled even if IAWEN = 0.

Address: F0078H After reset: 00H R/W

Symbol76543210

IAWCTL IAWEN 0 GRAM1 GRAM0 0 GPORT GINT GCSC

IAWEN

Note

Control of invalid memory access detection

0 Disable the detection of invalid memory access.

1 Enable the detection of invalid memory access.

Loading...

Loading...