2-14

IM DLM6054-01EN

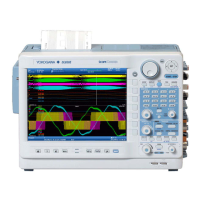

2.4 Displaying and Triggering on Logic Signals

The DL6000/DLM6000 can display and trigger on the 32-bit logic signal (16-bit on 16-bit models) that it

receives through its rear-panel logic signal input ports.

section 5.2 for the procedure

When you turn on the logic signal display, the screen is divided vertically in two. The logic signal area

is displayed below the normal analog waveform area.

Grouping

You can assign the 32 logic signal bits (16 on 16-bit models) to five different groups.

Display Order

You can set the order in which groups are displayed.

Vertical Display Range

You can set the vertical display range for logic signals.

Vertical Position

You can set the vertical display position of the logic signal in the logic signal area.

Bus Display

You can show bus displays for each group in hexadecimal or binary format.

State Display

With this feature, you can use the edges of a specified clock signal to trigger the acquisition of the

state of the input logic signal. Even if the logic signal changes, the state will not change until the

next clock edge.

section 5.2 for the procedure

For each logic signal bit, you can set the threshold level used to detect whether the logic signal is high

or low. The threshold level setting that you can select from are CMOS(5V), CMOS(3.3V), CMOS(2.5V),

CMOS(1.8V), ECL, and User (custom value).

section 5.2 for the procedure

You can view the signals after correcting the time offset (skew) between the logic signals and the other

signals.

Deskewing is performed on all bits collectively.

sections 6.3 to 6.13 for the procedure

As with analog signals, the DL6000/DLM6000 can trigger on logic signals. You can specify an edge,

qualified edge, state, pulse, state pulse, event cycle, event delay, or event sequence trigger. For

details about each trigger, see the explanations in section 2.3 and the various procedure explanations

for the triggers.

Loading...

Loading...