6241A/6242 DC Voltage Current Source/Monitor Operation Manual

6.5 Status Register Structure

6-12

2. Event Enable Register

Each Event Register has an Enable Register that decides which bit is to be enabled. The Enable Register

sets the relevant bit in decimal values.

• Service Request Enable Register setting: *SRE

• Standard Event Status Enable Register setting: *ESE

• Device Event Enable Register setting: DSE

(Example) Enables only the EOM bit of the Device-Event Register.

When the EOM bit of the Device Event Register is set to 1, the DSB bit of the Status

Byte Register is set to 1.

(Example) Enables the Status Byte Register’s DSB (Device Event Status Register summary) bit and

the ESB (Standard Event Status Register summary) bit.

When the DSB bit or the ESB bit are set to 1, the Status Byte Register’s MSS bit is set

to 1.

3. Status Byte Register

The Status Byte Register summarizes the information from the Status Register. And, this Status Byte

Register’s summary is transmitted as a service request to the controller. Consequently, the function of

the Status Byte Register is slightly different from that of the Status Register structure. The Status Byte

Register is explained in the following:

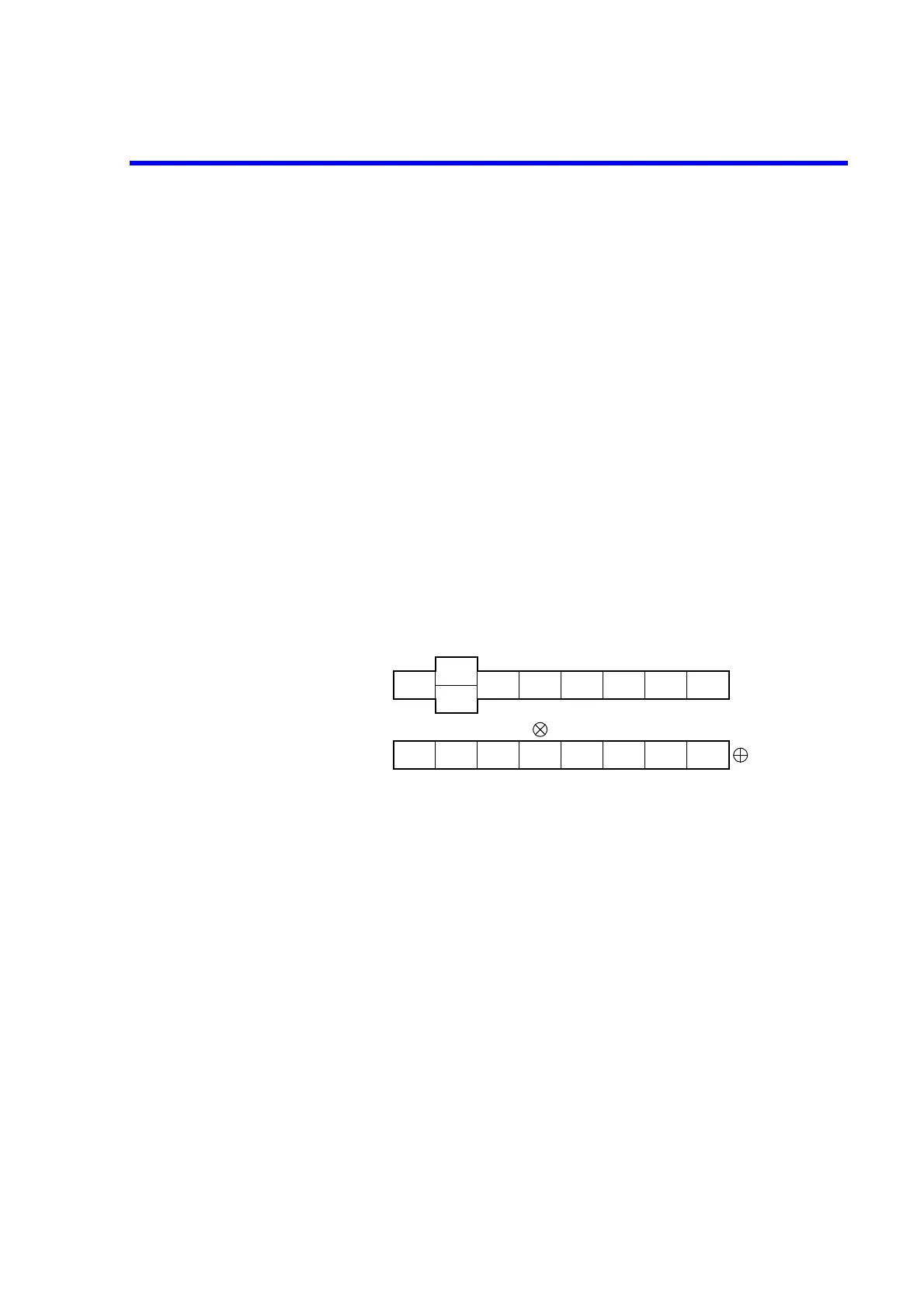

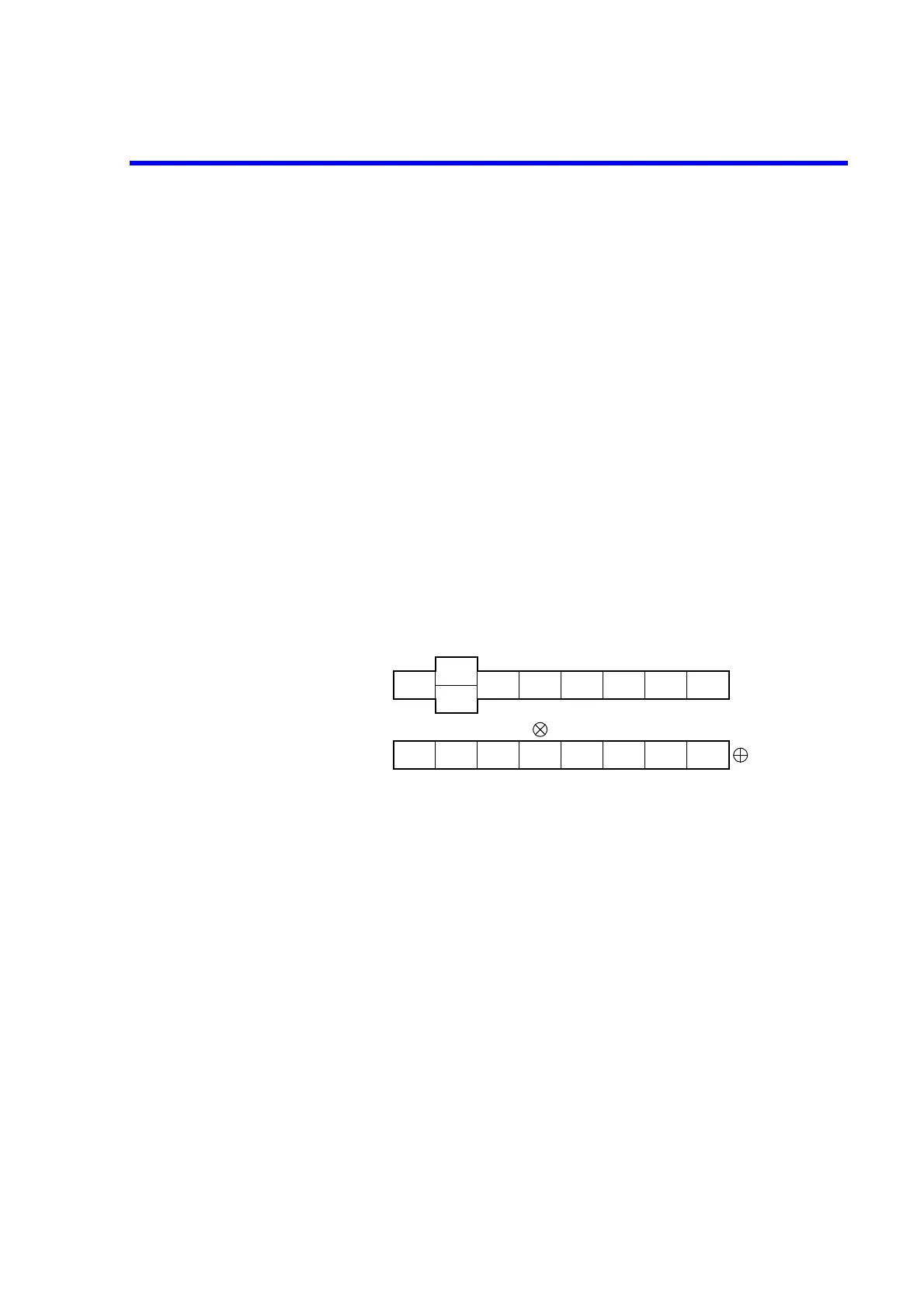

Figure 6-2 below shows the structure of the Status Byte Register.

Figure 6-2 Structure of Status Byte Register

The Status Byte Register is similar to the Status Register except for the following 3 points.

• The Summary of the Status Byte Register is written into bit 6 of the Status Byte Register.

• The Enable Register’s bit 6 is always enabled and cannot be changed.

• The Status Byte Register’s bit 6 (MSS) writes the RQS of the service request.

This register responds to the serial poll from the controller.

When responding to the serial poll, bit 0 to 5 of the Status Byte Register, bit 7, and RQS, are read, after

which RQS is reset to 0. Other bits are not cleared until their factors become 0.

The Status Byte Register, RQS, and MSS can be cleared by executing “*CLS.” Accompanying this, the

SRQ line also becomes False.

Table 6-3 below describes each bit of the Status Byte Register.

Status Byte Register

Service Request Enable

Register

♦ MSS

MSS

RQS

ESB

DSBMAV 2 1

7X

543

210

Loading...

Loading...