602

S:\Hp8960\E1962B CDMA 2000\Pi Release\Reference Guide\Chapters\cdma2000_hpib_status_questionable.fm

STATus:QUEStionable

STATus:QUEStionable Condition Register Bit Assignment

The STATus:QUEStionable register contains bits which give an indication that the data currently being

acquired or generated is of questionable quality due to some condition affecting the functionality associated

with that bit.

Program Example - STATus:QUEStionable Register Bit Assignments

OUTPUT 714;”STATUS:QUESTIONABLE:EVENT?” !Queries and clears the Questionable Event

!Register

OUTPUT 714;”STATUS:QUESTIONABLE:CONDITION?” !Queries and clears the Questionable Condition

!Register

OUTPUT 714;”STATUS:QUESTIONABLE:ENABLE 1024” !Sets the Questionable Enable Register

!for bit 10

OUTPUT 714;”STATUS:QUESTIONABLE:NTRANSITION 2” !Sets the Questionable Negative

!Transition Filter Register for bit 1

OUTPUT 714;”STATUS:QUESTIONABLE:PTRANSITION 2” !Sets the Questionable Positive

!Transition Filter Register for bit 1

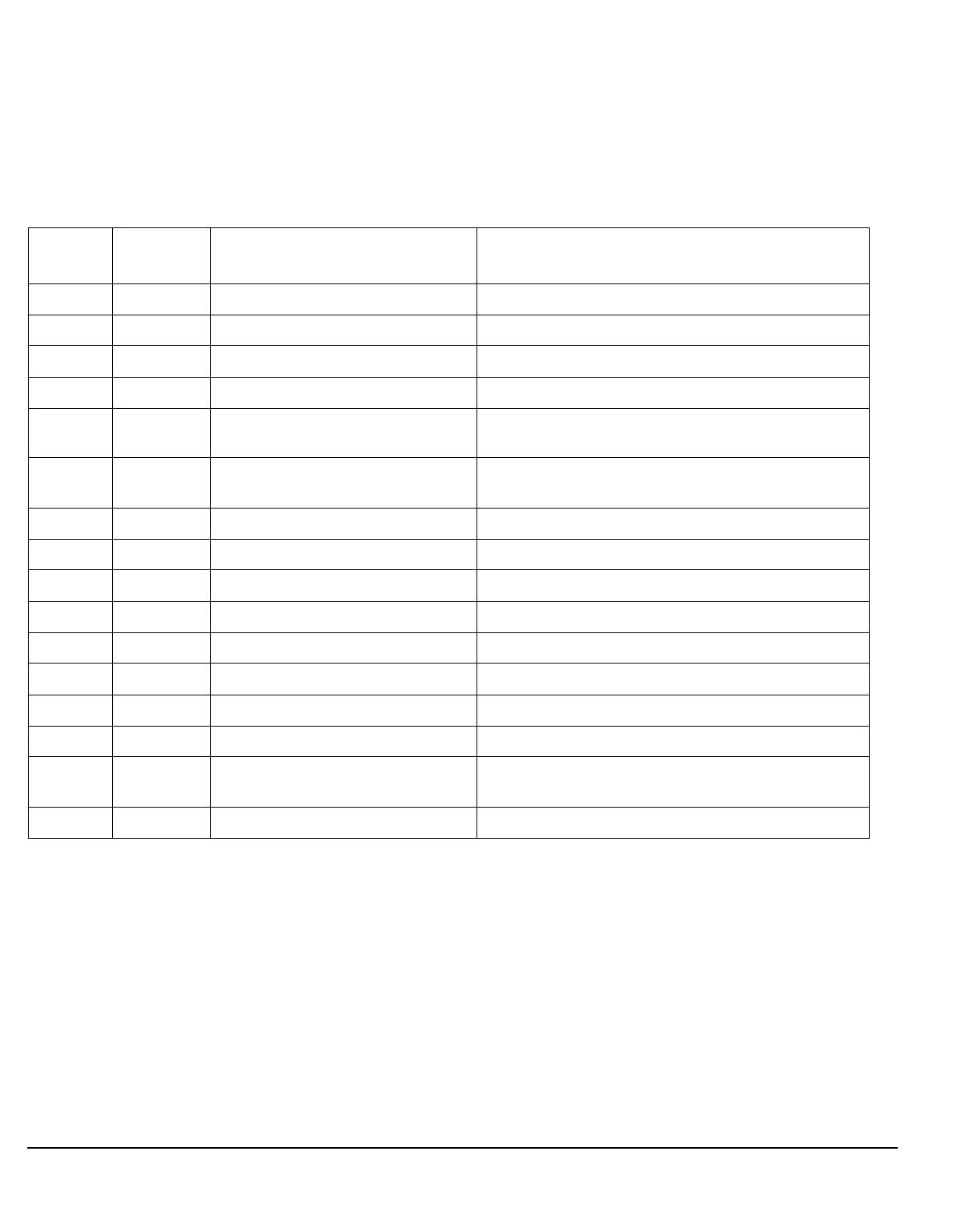

Bit

Number

Binary

Weighting

Condition Description

15 32768 Not Used. Defined by SCPI. This bit is always 0.

14 16384 Reserved for future use. This bit is always 0

13 8192 Reserved for future use. This bit is always 0.

12 4096 Reserved for future use. This bit is always 0.

11 2048 QUEStionable:HARDware

summary

This bit is the summary message bit for the

STATus:QUEStionable:HARDware register.

10 1024 QUEStionable:CALL summary This bit is the summary message bit for the

STATus:QUEStionable:CALL register.

9 512 Reserved for future use. This bit is always 0.

8 256 Reserved for future use. This bit is always 0.

7 128 Reserved for future use. This bit is always 0.

6 64 Reserved for future use. This bit is always 0.

5 32 Reserved for future use. This bit is always 0.

4 16 Reserved for future use. This bit is always 0.

3 8 Reserved for future use. This bit is always 0.

2 4 Reserved for future use. This bit is always 0.

1 2 QUEStionable:ERRors summary This bit is the summary message bit for the

STATus:QUEStionable:ERRors register.

0 1 Reserved for future use. This bit is always 0.

Loading...

Loading...