Chapter 4 INTERFACE SETTINGS

123

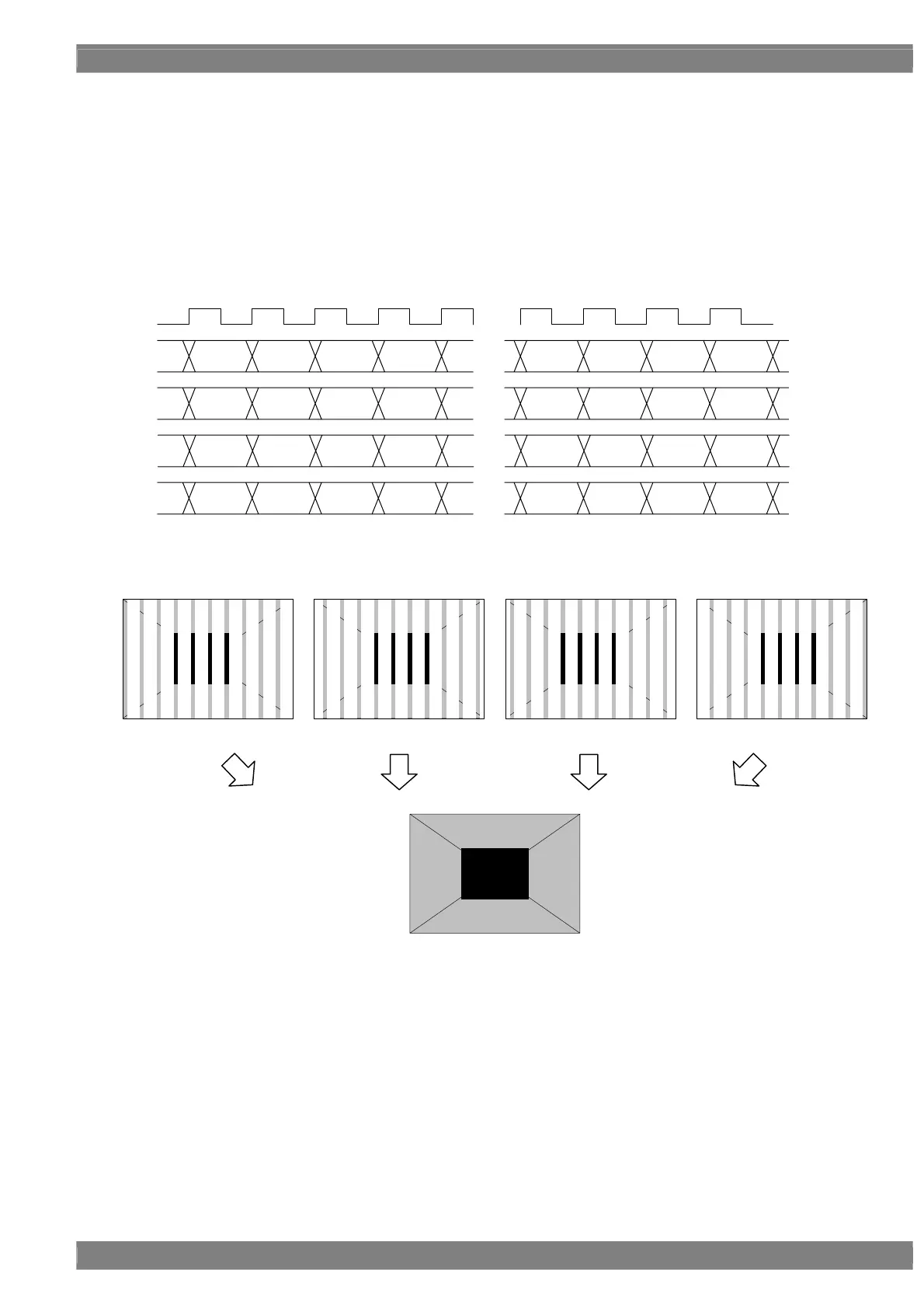

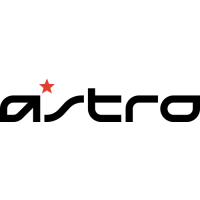

[5] MODE4 (Quad Link ) (no dividing)

Using channel 1 and 2, EVEN pixels are output. Using channel 3 and 4, ODD pixels are output.

Given here as an example of the resolution is 4096 × 2048, the dot clock frequency is 592 MHz with the 10 bits

output.

CLK

148MHz

1CH

4CH

・・・

L0~L2047

L0~L2047

[9:0] [9:0] [9:0] [9:0]

D 0

[9:0]

・・・

[9:0] [9:0] [9:0]

D 3

D 4092

[9:0]

D 4095

[9:0] [9:0] [9:0]

[9:0]

・・・

[9:0] [9:0] [9:0]

D 4

D 7

D 8

D 11

D 12

D 15

D 4088

D 4091

D 4084

D 4087

D 4080

D 4083

2CH

L0~L2047

D 1

[9:0] [9:0] [9:0] [9:0][9:0]

・・・

[9:0] [9:0] [9:0]

D 4093D 5 D 9 D 13 D 4089D 4085D 4081

3CH

L0~L2047

[9:0] [9:0] [9:0] [9:0][9:0]

D 2

・・・

[9:0] [9:0] [9:0]

D 4094D 6 D 10 D 14 D 4090D 4086D 4082

1CH 2CH 3CH 4CH

Loading...

Loading...