RL78/G1H CHAPTER 6 CLOCK GENERATOR

R01UH0575EJ0120 Rev. 1.20 Page 133 of 920

Dec 22, 2016

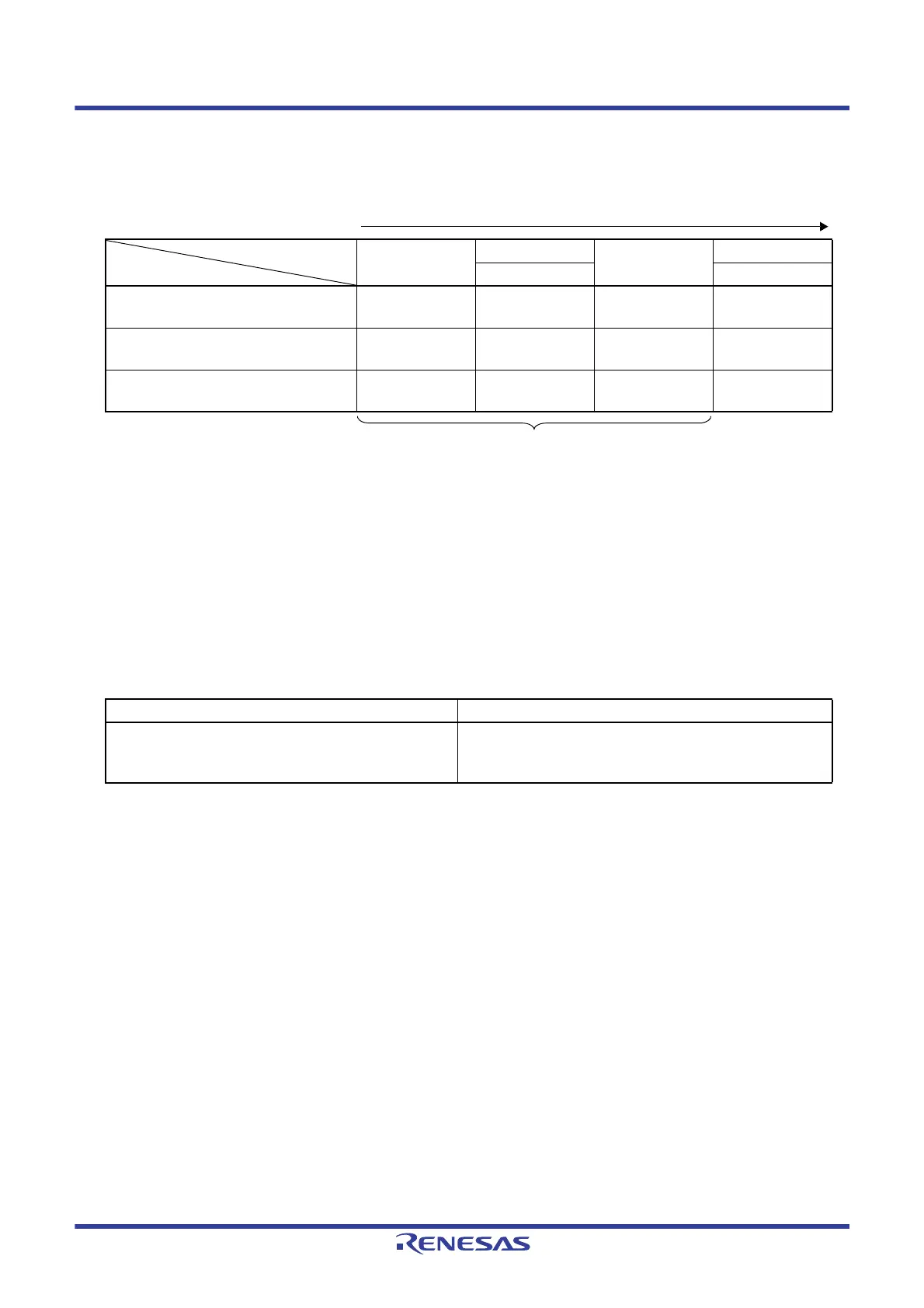

Table 6 - 6 CPU Clock Transition and SFR Register Setting Examples (4/5)

(9) CPU clock changing from subsystem clock (D) to high-speed system clock (C)

Note Set the oscillation stabilization time as follows.

• Desired the oscillation stabilization time counter status register (OSTC) oscillation stabilization time

≤ Oscillation

stabilization time set by the oscillation stabilization time select register (OSTS)

Caution Set the clock after the supply voltage has reached the operable voltage of the clock to be set (see CHAPTER 31

ELECTRICAL SPECIFICATIONS).

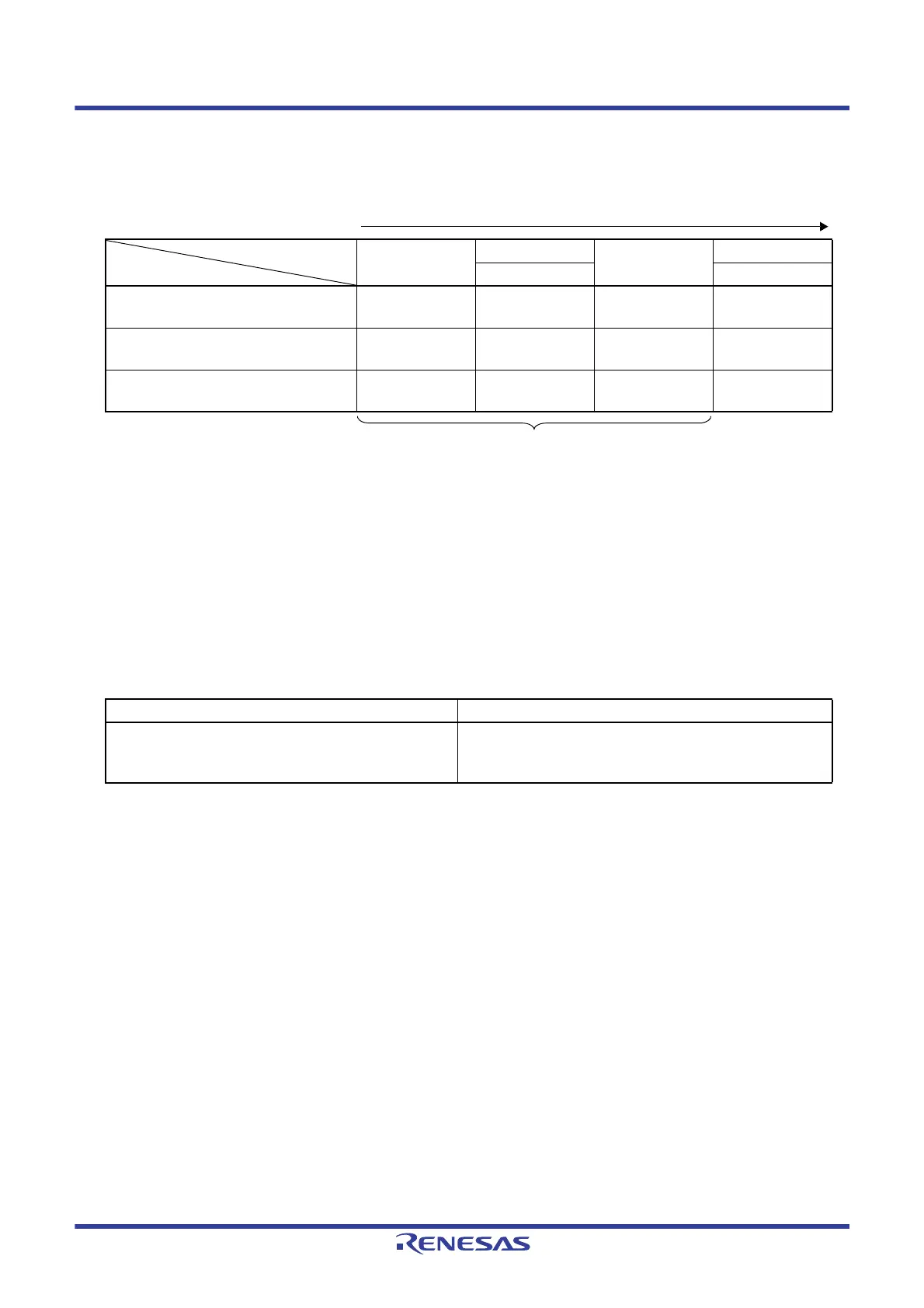

(10) • HALT mode (E) set while CPU is operating with high-speed on-chip oscillator clock (B)

• HALT mode (F) set while CPU is operating with high-speed system clock (C)

• HALT mode (G) set while CPU is operating with subsystem clock (D)

Remark (A) to (J) in Tables 6 - 3 to 6 - 7 correspond to (A) to (J) in Figure 6 - 19.

(Setting sequence of SFR registers)

Setting Flag of SFR Register

OSTS Register

CSC Register

OSTC Register

CKC Register

Status Transition MSTOP CSS

(D)

→ (C)

(X1 clock: 1 MHz

≤ fX ≤ 10 MHz)

Note

0 Must be checked 0

(D)

→ (C)

(X1 clock: 10 MHz < f

X ≤ 20 MHz)

Note

0 Must be checked 0

(D)

→ (C) (external main clock)

Note

0

Need not be

checked

0

Unnecessary if the CPU is operating with

the high-speed system clock

Status Transition Setting

(B)

→ (E)

(C)

→ (F)

(D)

→ (G)

Executing HALT instruction

Loading...

Loading...