RL78/G1H CHAPTER 7 TIMER ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 179 of 920

Dec 22, 2016

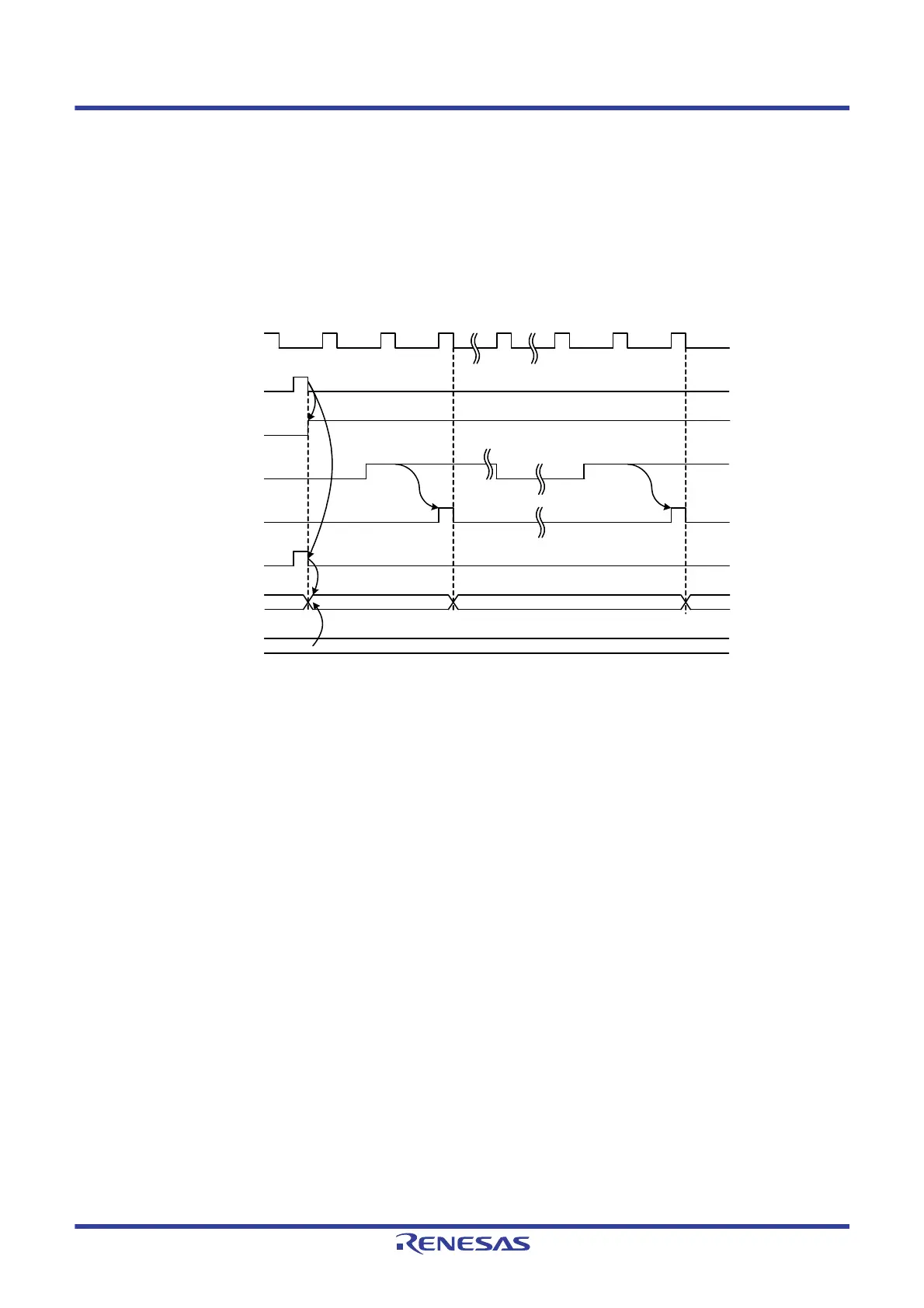

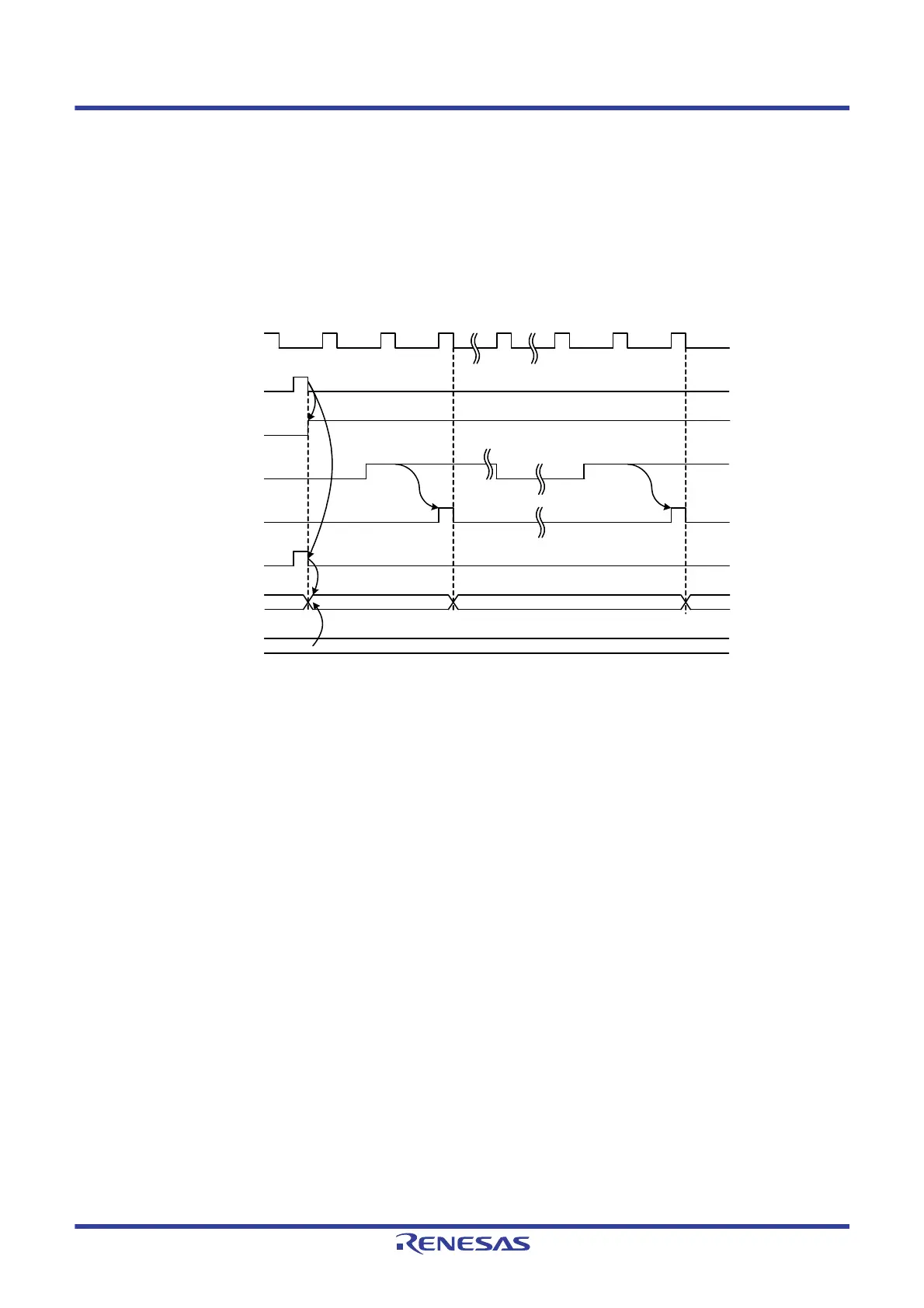

(2) Operation of event counter mode

<1> Timer count register mn (TCRmn) holds its initial value while operation is stopped (TEmn = 0).

<2> Operation is enabled (TEmn = 1) by writing 1 to the TSmn bit.

<3> As soon as 1 has been written to the TSmn bit and 1 has been set to the TEmn bit, the value of timer

data register mn (TDRmn) is loaded to the TCRmn register to start counting.

<4> After that, the TCRmn register value is counted down according to the count clock of the valid edge of

the TImn input.

Figure 7 - 29 Operation Timing (In Event Counter Mode)

Remark The timing is shown in Figure 7 - 29 indicates while the noise filter is not used. By making the noise filter on-

state, the edge detection becomes 2 f

MCK cycles (it sums up to 3 to 4 cycles) later than the normal cycle of

TImn input. The error per one period occurs be the asynchronous between the period of the TImn input and

that of the count clock (f

MCK).

fMCK

TSmn (Write)

TEmn

TImn input

Count clock

Start trigger

detection signal

<1>

<2>

<4>

Edge detection Edge detection

TCRmn

TDRmn

<3>

<3>

<1>

Initial value

mm -1m -2

m

Loading...

Loading...