RL78/G1H CHAPTER 7 TIMER ARRAY UNIT

R01UH0575EJ0120 Rev. 1.20 Page 217 of 920

Dec 22, 2016

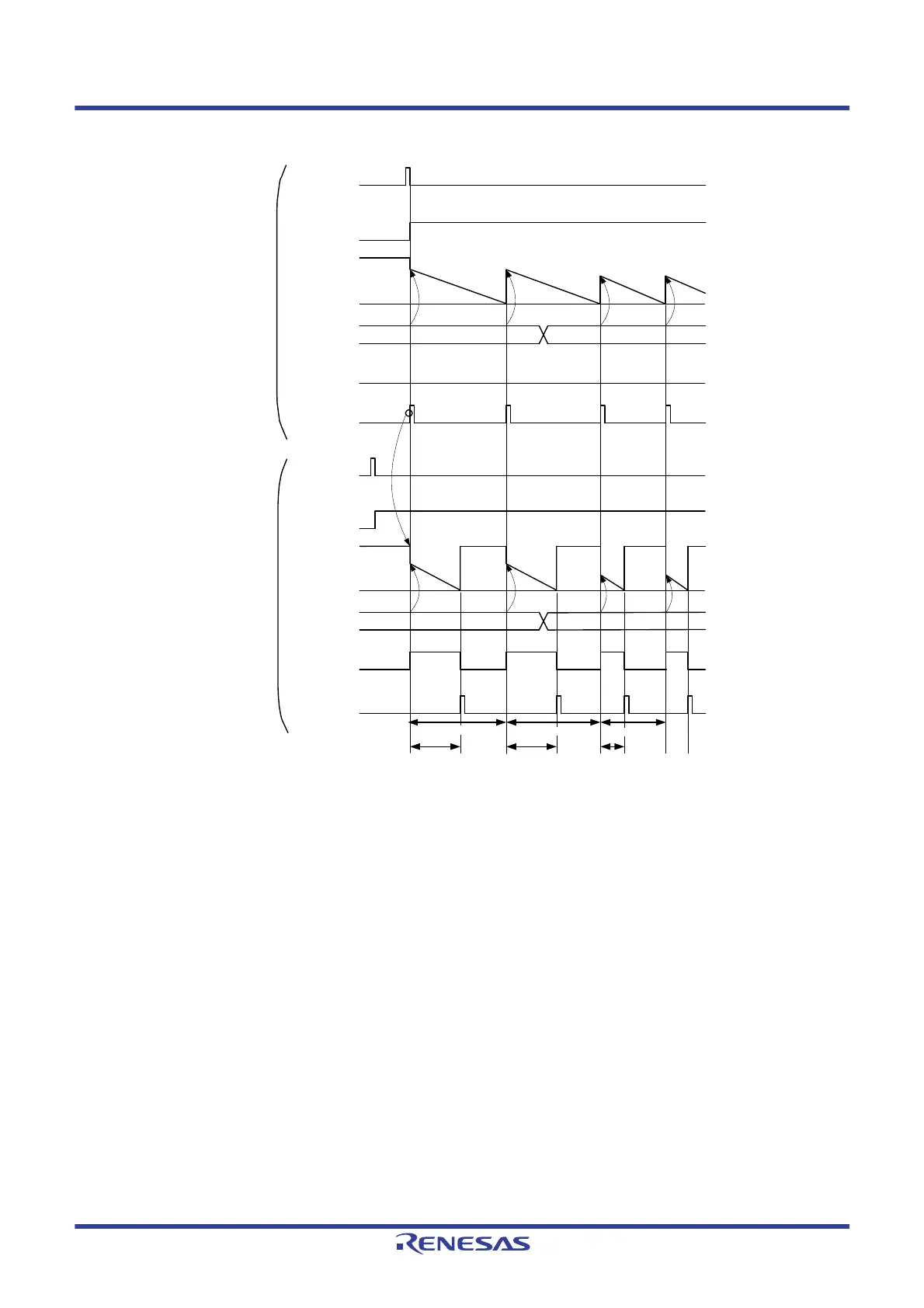

Figure 7 - 64 Example of Basic Timing of Operation as PWM Function

Remark 1. m: Unit number (m = 0), n: Master channel number (n = 0, 2)

p: Slave channel number (p = 3)

Remark 2. TSmn, TSmp: Bit n, p of timer channel start register m (TSm)

TEmn, TEmp: Bit n, p of timer channel enable status register m (TEm)

TCRmn, TCRmp: Timer count registers mn, mp (TCRmn, TCRmp)

TDRmn, TDRmp: Timer data registers mn, mp (TDRmn, TDRmp)

TOmn, TOmp: TOmn and TOmp pins output signal

TSmn

TEmn

TDRmn

TCRmn

TOmn

INTTMmn

a b

TSmp

TEmp

TDRmp

TCRmp

TOmp

INTTMmp

c

d

a + 1

c

a + 1 b + 1

c d

FFFFH

0000H

FFFFH

0000H

Master

channel

Slave

channel

Loading...

Loading...